Hybrid Beamforming Processor for mmWave MIMO Systems

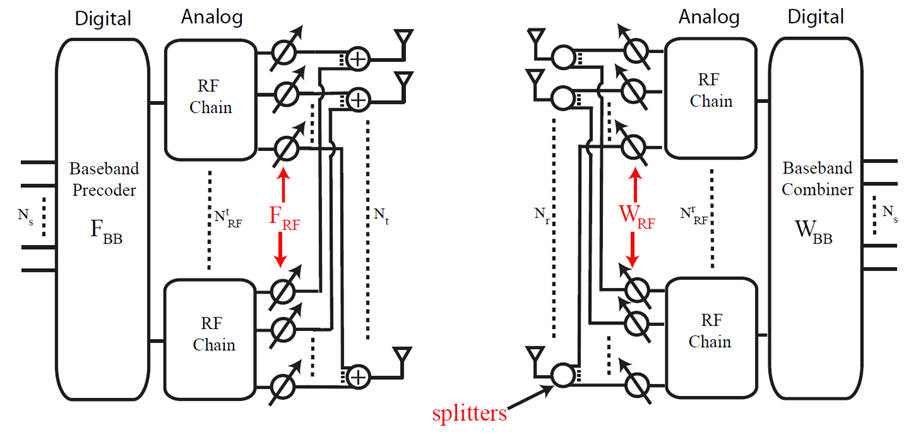

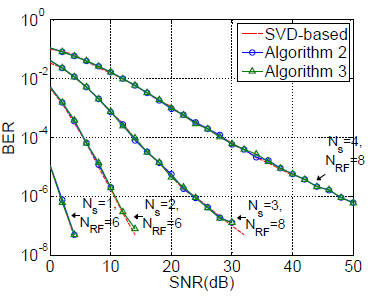

Millimeter wave (mmWave) system is an emerging transmission technique to improve the reliability and transmitted quality for the future 5G communication systems. MIMO beamforming technique can use the RF phase controller to achieve high-resolution spatial transmission channel to overcome the problems of path-loss and high-correlation of the mmWave channel. Our research focuses on hybrid RF/baseband beamforming for the mmWave MIMO systems. The DSP algorithms/processors are designed to build up the optimal RF beam-forming phase array vector and baseband MIMO precoding matrix. This approach can reduce the RF chain number and the power consumption of the analog front-end for massive MIMO systems.

Research Topics: Wideband mmWave Hybrid Beamforming, 5G Baseband Processor VLSI

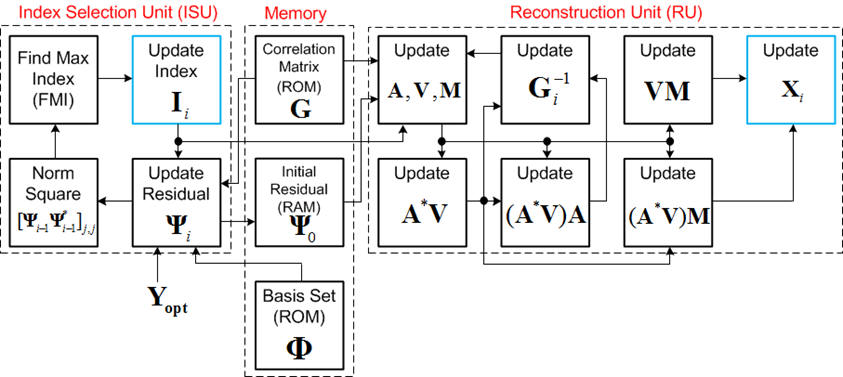

- Yun-Yueh Lee, Ching-Hung Wang, and Yuan-Hao Huang, “A Hybrid RF/Baseband Precoding Processor Based on Parallel-Index-Selection Matrix-Inversion-Bypass Simultaneous Orthogonal Matching Pursuit for Millimeter Wave MIMO Systems,” IEEE Transaction on Signal Processing, vol. 63, no. 2, pp.305-317, Feb. 2015.

- Cheng-Kang Ho, Hao-Yu Cheng, and Yuan-Hao Huang, “Hybrid Precoding Processor for Millimeter Wave MIMO Communications,” IEEE Transactions on Circuits and Systems II : Express Briefs, vol. 66, no.12, pp.1992-1996, Dec. 2019.

- Hao-Yu Cheng, Chen-Wei Chen, Chung-An Shen, and Yuan-Hao Huang, “The Configurable Hybrid Precoding Processor for Bit-Stream-Based mmWave MIMO Systems,” IEEE Transaction on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 12, pp. 2612-2622, Dec. 2020.

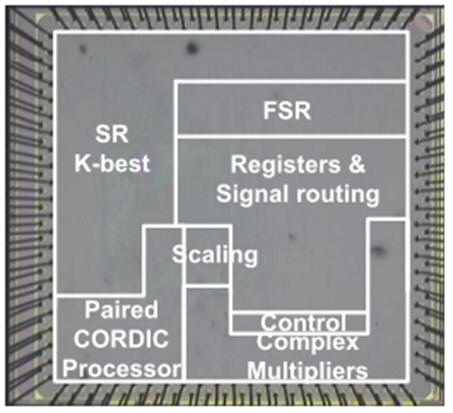

MIMO Preprocessing and Detection Processors

Spatial multiplexing multiple-input and multiple-output is an important technique for improving the transmission capacity of a communication system. The receiver must mitigate the interference between antennas and detect the transmitted symbols by processing MIMO channel matrix and detecting the constellation symbols. Our research designs hardware-oriented MIMO preprocessing and signal processing algorithms and architecture and implements byw FPGA or ASIC chips.

Research topics: Quantized Precoding for massive MIMO,

- Chun-Fu Liao and Yuan-Hao Huang, “Power-Saving 4×4 Lattice Reduction Processor for MIMO Detection with Redundancy Checking,” IEEE Trans. Circuits and Systems II – Express Briefs, vol. 58, no.2, pp.95-99, Feb, 2011.

- Chun-Fu Liao, Fung-Chun Lan, Jin-Wei Jhang, and Yuan-Hao Huang, “A 576Mbps 64-QAM 4×4 MIMO Precoding Processor with Lattice Reduction,” IEEE Trans. Circuits and Systems II – Express Briefs, vol. 61, no. 2, pp.95-99 Feb. 2014.