# Introduction Why DFT? What is DFT? Ad-Hoc Approaches Full Scan Partial Scan

# Why DFT?

- Direct Testing is Way Too Difficult!

- Large number of FFs

- Embedded memory blocks

- Embedded analog blocks

- Design For Testability is inevitable

- · Like death and tax

ch5-3

# Design For Testability

- Definition

- Design For Testability (DFT) refers to those design techniques that make test generation and testing cost-effective

- DFT Methods

- Ad-hoc methods

- Scan, full and partial

- Built-In Self-Test (BIST)

- Boundary scan

- Cost of DFT

- Pin count, area, performance, design-time, test-time

# Why DFT Isn't Universally Used Previously?

- Short-sighted view of management

- Time-to-market pressure

- Life-cycle cost ignored by development management/contractors/buyers

- Area/functionality/performance myths

- Lack of knowledge by design engineers

- Testing is someone else's problem

- Lack of tools to support DFT until recently

We don't' have to worry about this management barrier any more

→ Most design teams now have DfT people

ch5-5

# **Important Factors**

- Controllability

- Measure the ease of controlling a line

- Observability

- Measure the ease of observing a line at PO

- Predictability

- Measure the ease of predicting output values

- DFT deals with ways of improving

- Controllability

- Observability

- Predictability

### Outline

- Introduction

- Ad-Hoc Approaches

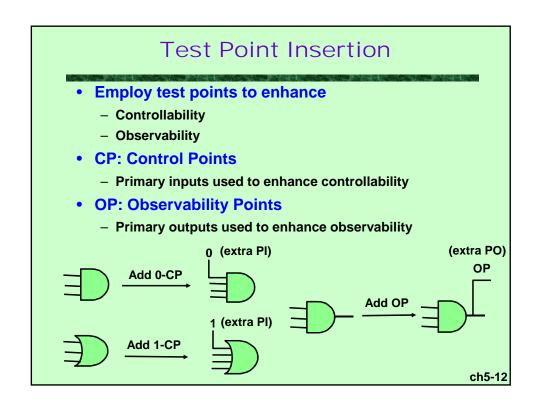

- Test Points

- Design Rules

- Full Scan

- Partial Scan

ch5-7

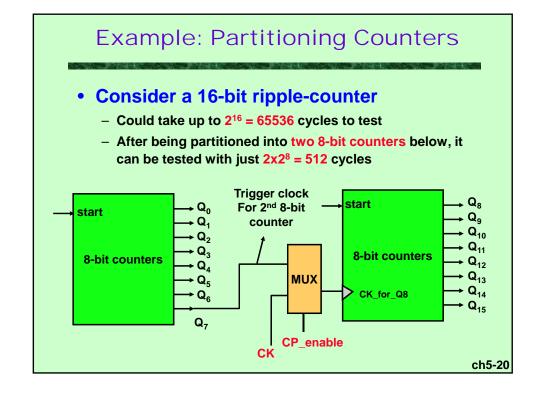

# Ad-Hoc Design For Testability

- Design Guidelines

- Avoid redundancy

- Avoid asynchronous logic

- Avoid clock gating (e.g., ripple counter)

- Avoid large fan-in

- Consider tester requirements (tri-stating, etc.)

- Disadvantages

- High fault coverage not guaranteed

- Manual test generation

- Design iterations required

### Some Ad-Hoc DFT Techniques Test Points Initialization Delay outpu Monostable multivibrators - One-shot circuit Oscillators and clocks One-shot Counters / Shift-Registers - Add control points to long counters input Partition large circuits output Logical redundancy · Break global feedback paths ch5-9

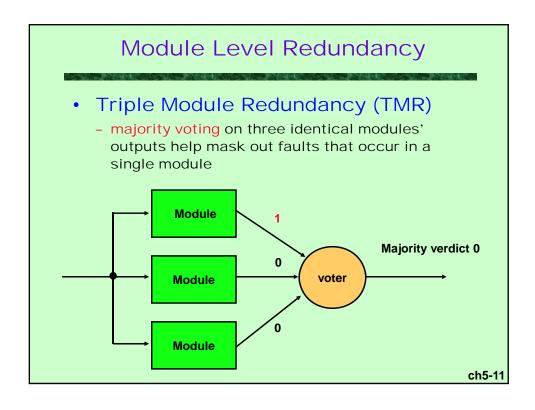

# On-Line Self-Test & Fault Tolerance By Redundancy

### Information Redundancy

- Outputs = (information-bits) + (check-bits)

- Information bits are the original normal outputs

- Check bits always maintains a specific pre-defined logical or mathematical relationship with the corresponding information bits

- Any time, if the information-bits and check-bits violate the pre-defined relationship, then it indicates an error

### Hardware Redundancy

Use extra hardware (e.g., duplicate or triplicate the system) so that the fault within one module will be masked (I.e., the faulty effect never observed at the final output)

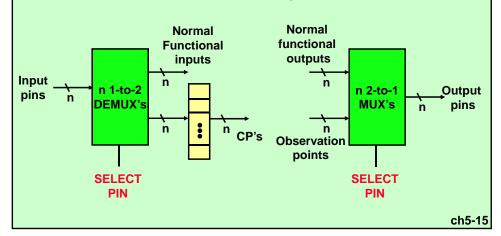

# O/1 Injection Circuitry Normal operation When CP\_enable = 0 Inject 0 Set CP\_enable = 1 and CP = 0 Inject 1 Set CP\_enable = 1 and CP = 1

7

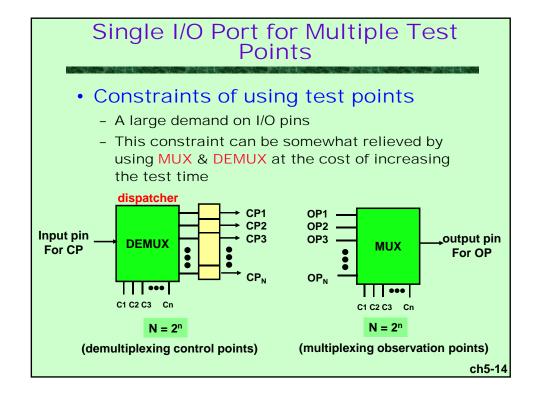

# Sharing Between Test Points & Normal I/O

- Advantage: Even fewer I/O pins for Test Points

- Overhead: Extra MUX delay for normal I/O

### **Control Point Selection**

- Impact

- The controllability of the fanout-cone of the added point is improved

- Common selections

- Control, address, and data buses

- Enable / Hold inputs

- Enable and read/write inputs to memory

- Clock and set/clear signals of flip-flops

- Data select inputs to multiplexers and demultiplexers

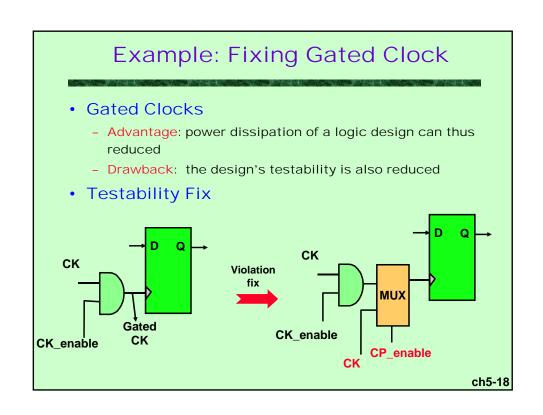

# Example: Use CP to Fix DFT Rule Violation DFT rule violations - The set/clear signal of a flip-flop is generated by other logic, instead of directly controlled by an input pin - Gated clock signals Violation Fix - Add a control point to the set/clear signal or clock signals Q Violation CKclear

logic

CLEAR

ch5-17

CK -

logic

clear

# Example: Fixing Tri-State Bus Contention Bus Contention A stuck-at-fault at the tri-state enable line may cause bus contention – multiple active drivers are connected to the bus simultaneously Fix Add CPs to turn off tri-state devices during testing (A Bus Contention Scenario in the presence of a fault) Enable line stuck-at-1 Unpredictable voltage on bus may cause a fault to go unnoticed

### **Observation Point Selection**

- Impact

- The observability of the fanin-cone (or transitive fanins) of the added OP is improved

- Common choice

- Stem lines having a large number of fanouts

- Global feedback paths

- Redundant signal lines

- Output of logic devices having many inputs

- MUX, XOR trees

- Output from state devices

- Address, control and data buses

(常為電路區塊間之介面訊號)

### Outline

- Introduction

- Ad-Hoc Approaches

- Full Scan

- The Concept

- Scan Cell Design

- Random Access Scan

- Partial Scan

ch5-23

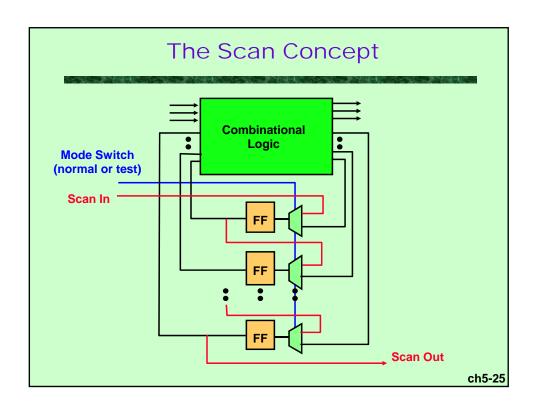

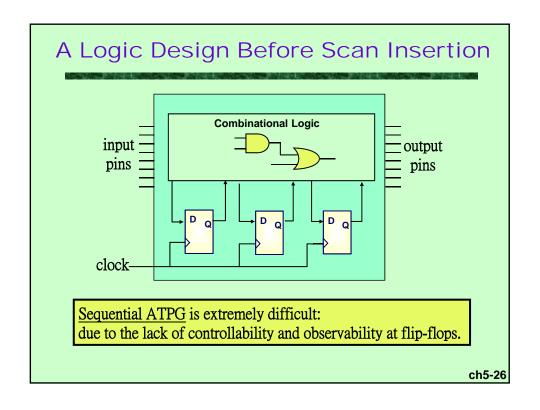

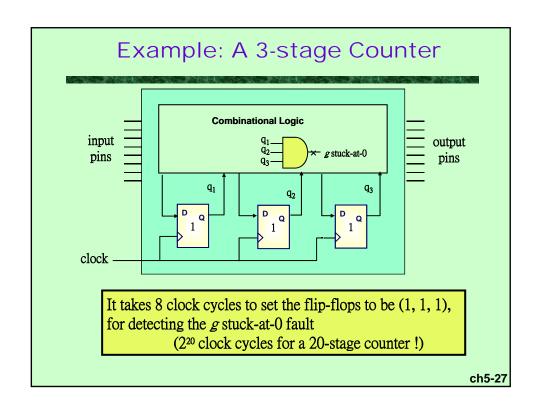

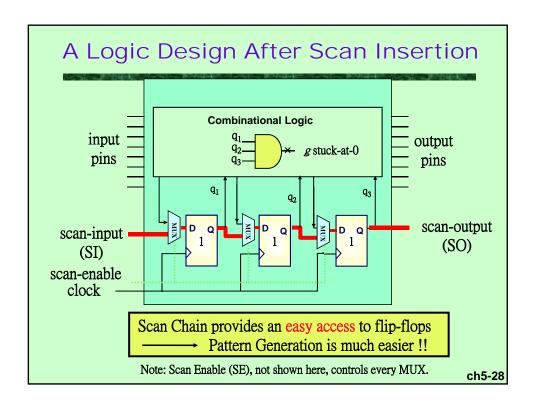

### What Is Scan?

### • Objective

- To provide controllability and observability at internal state variables for testing

- Method

- Add test mode control signal(s) to circuit

- Connect flip-flops to form shift registers in test mode

- Make inputs/outputs of the flip-flops in the shift register controllable and observable

- Types

- Internal scan

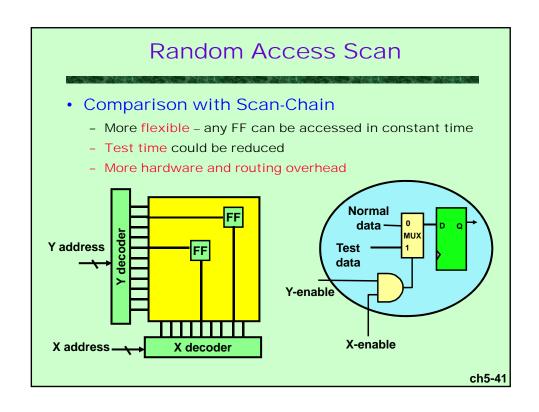

- Full scan, Partial scan, Random access

- Boundary scan

# **Procedure of Applying Test Patterns**

Pl's

PPI's -

Comb.

portion

### Notation

- Test vectors  $T = \langle t_i^I, t_i^F \rangle i = 1, 2, ...$

- Output Response  $R = \langle r_i^0, r_i^F \rangle i = 1, 2, ...$

### Test Application

- (1) i = 1;

- (2) Scan-in t<sub>1</sub>F /\* scan-in the first state vector for PPI's \*/

- (3) Apply t<sub>i</sub><sup>I</sup> /\* apply current input vector at PI's \*/

- (4) Observe r<sub>i</sub><sup>O</sup> /\* observe current output response at PO's \*/

- (5) Capture PPOs to FFs as r<sub>i</sub>F/\* capture the response at PPO's to FFs \*/

- (Set to 'Normal Mode' by raising SE to '1' for one clock cycle)

- (6) Scan-out  $r_{i}^{\,F}$  while scanning-in  $t_{i+1}^{\,F}/^{*}$  overlap scan-in and scan-out  $^{*}/$

- (7) i = i+1; Goto step (3)

ch5-29

PO's

PPO's

# Testing Scan Chain?

### Common practice

- Scan chain is often first tested before testing the core logic by a so-called flush test - which pumps random vectors in and out of the scan chain

- Procedure (flush test of scan chain)

- (1) i = 0;

- (2) Scan-in 1st random vector to flip-flops

- (3) Scan-out (i)<sup>th</sup> random vector while scanning-in (i+1)<sup>th</sup> vector for flip-flops.

- The (i)<sup>th</sup> scan-out vector should be identical to (i)<sup>th</sup> vector scanned in earlier, otherwise scan-chain is mal-functioning

- (4) If necessary i = i+1, goto step (3)

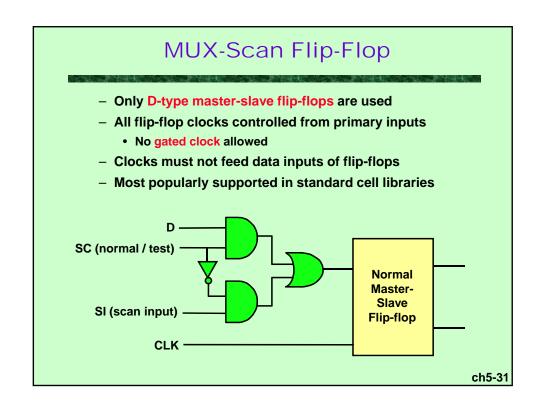

### Some Problems With Full Scan

- Problems

- Area overhead

- Synopsys Mentor-Graphics SynTest (華騰科技) Cadence

**Major Commercial Test Tool Companies**

- Possible performance degradation

- High test application time

- Power dissipation

- Features of Commercial Tools

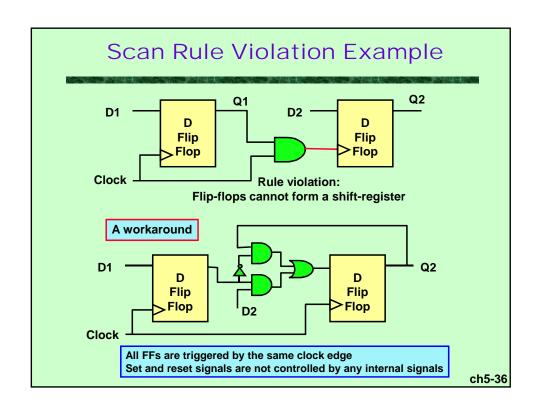

- Scan-rule violation check (e.g., DFT rule check)

- Scan insertion (convert a FF to its scan version)

- ATPG (both combinational and sequential)

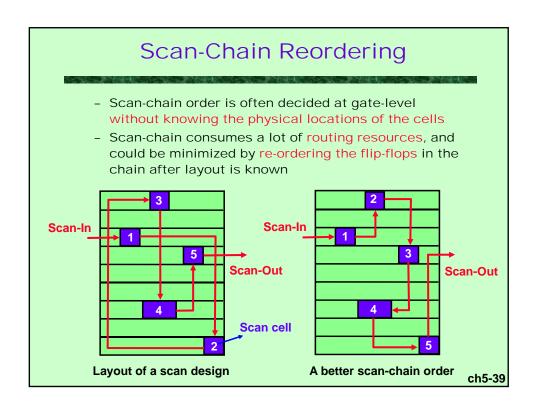

- Scan chain reordering after layout

ch5-37

### Performance Overhead

- The increase of delay along the normal data paths include:

- Extra gate delay due to the multiplexer

- Extra delay due to the capacitive loading of the scan-wiring at each flip-flop's output

- Timing-driven partial scan

- Try to avoid scan flip-flops that belong to the timing critical paths

- The flip-flop selection algorithm for partial scan can take this into consideration to reduce the timing impact of scan to the design

# Overhead of Scan Design

- Number of CMOS gates = 2000

- Fraction of flip-flops = 0.478

| Scan<br>implementation | Predicted overhead | Actual area overhead | Normalized operating frequency |

|------------------------|--------------------|----------------------|--------------------------------|

| None                   | 0                  | 0                    | 1.0                            |

| Hierarchical           | 14.05%             | 16.93%               | 0.87                           |

| Optimized              | 14.05%             | 11.9%                | 0.91                           |

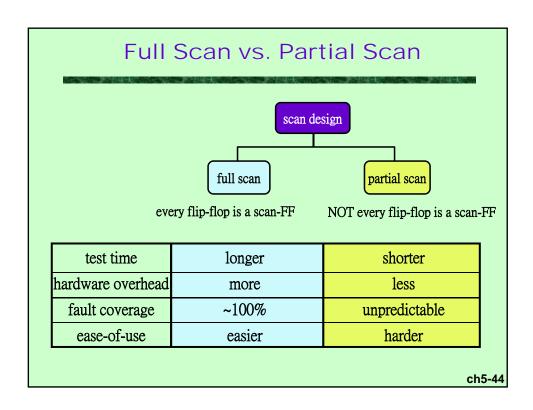

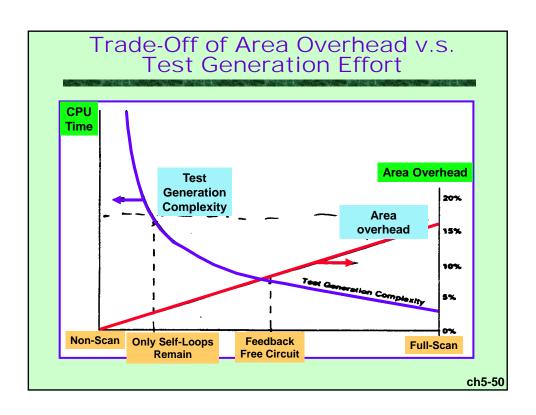

### Partial Scan

- · Basic idea

- Select a subset of flip-flops for scan

- Lower overhead (area and speed)

- Relaxed design rules

- Cycle-breaking technique

- Cheng & Agrawal, IEEE Trans. On Computers, April 1990

- Select scan flip-flops to simplify sequential ATPG

- Overhead is about 25% off than full scan

- Timing-driven partial scan

- Jou & Cheng, ICCAD, Nov. 1991

- Allow optimization of area, timing, and testability simultaneously

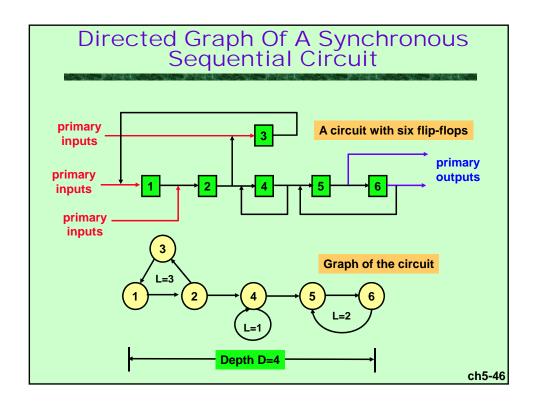

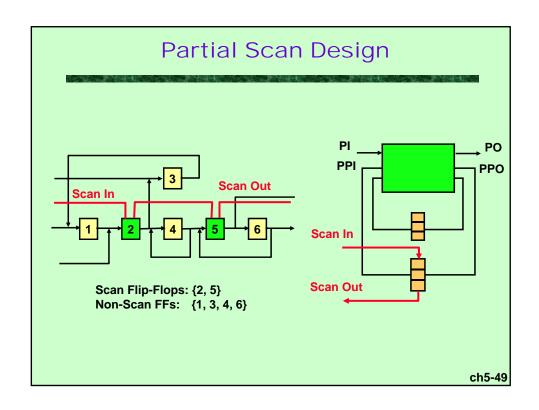

## Partial Scan For Cycle-Free Structure

- Select minimal set of flip-flops

- To eliminate some or all cycles

- Self-loops of unit length

- Are not broken to reduce scan overhead

- The number of self-loops in real design can be quite large

- · Limit the length of

- Consecutive self-loop paths

- Long consecutive self-loop paths in large circuits may pose problems to sequential ATPG

ch5-47

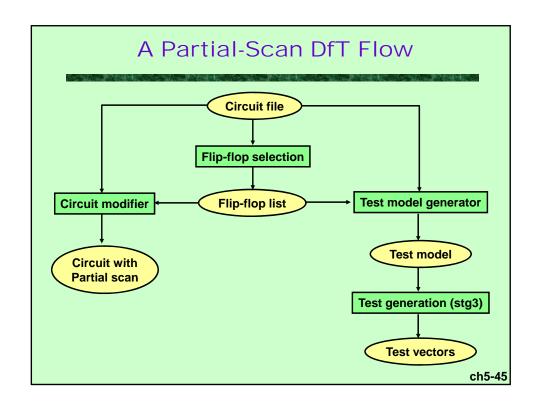

### Test Generation for Partial Scan Circuits

- Separate scan clock is used

- · Scan flip-flops are removed

- And their input and output signals are added to the PO/PI lists

- · A sequential circuit test generator

- is used for test generation

- The vector sequences

- Are then converted into scan sequences

- Each vector is preceded by a scan-in sequence to set the states of scanned flip-flops

- A scan-out sequence is added at the end of applying each vector

# Summary of Partial-Scan

- Partial Scan

- Allows the trade-off between test generation effort and hardware overhead to be automatically explored

- Breaking Cycles

- Dramatically simplifies the sequential ATPG

- Limiting the Length of Self-Loop Paths

- Is crucial in reducing test generation effort for large circuits

- Performance Degradation

- Can be minimized by using timing analysis data for flip-flop selection