### 國立清華大學電機系

EE-6250 超大型積體電路測試 VLSI Testing

# **Chapter 10 High-Speed Interconnect Testing**

#### **Outline**

- **♦** Introduction

- ◆ Problem, Objective, Review, and Motivation

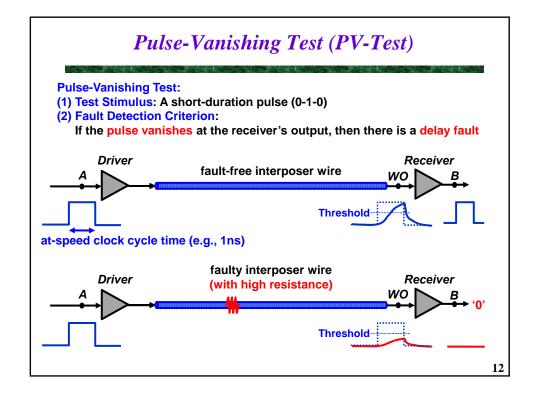

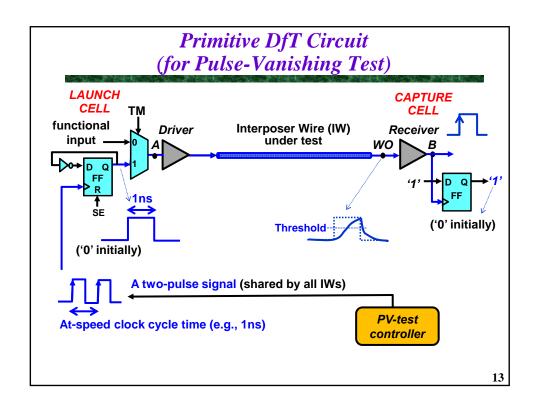

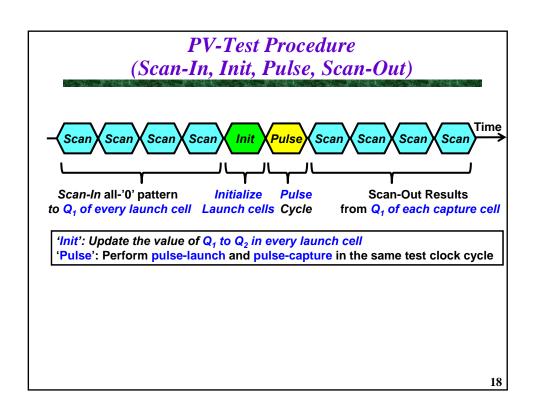

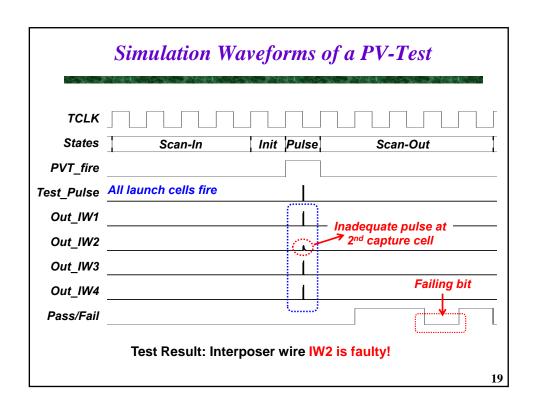

- **♦** Pulse-Vanishing Test (PV-Test)

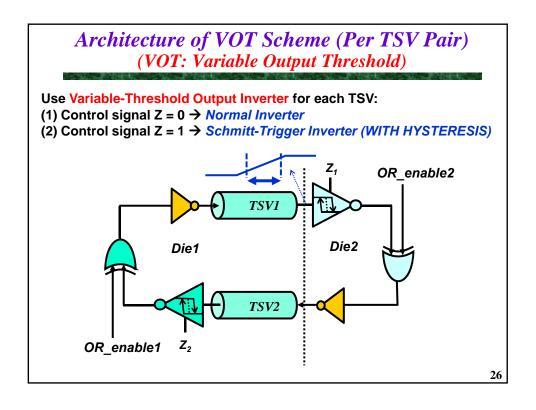

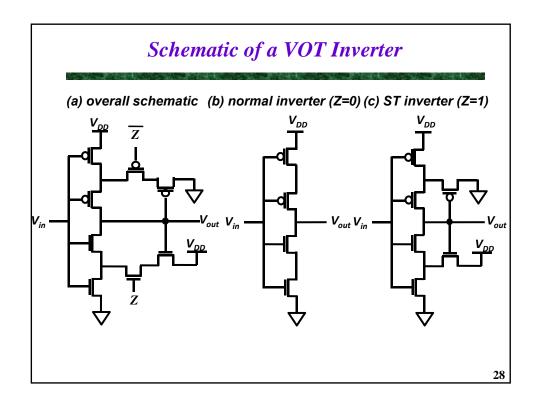

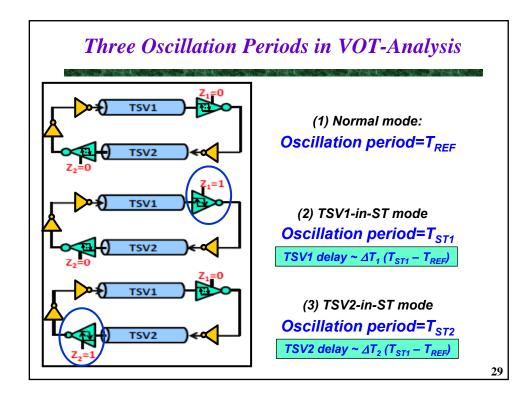

- **♦ VOT-Based Oscillation Test**

## Objective and Challenge

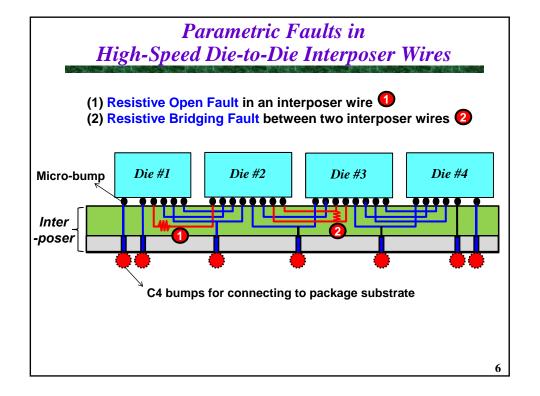

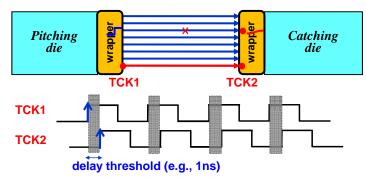

Objective: To detect parametric faults (e.g., <1ns delay fault)

- → May need to maintain a <u>pitcher-catcher timing relationship</u> across dies (This type of cross-die clock synchronization may not be easy)

- → There are so other choices...

Note: test clocks TCK1 and TCK2 are low-speed test clocks (e.g., 10MHz)

7

#### **Outline**

- **♦** Introduction

- → Pulse-Vanishing Test (PV-Test)

- At-speed testing for high-speed interconnects

- **♦ VOT-Based Oscillation Test**

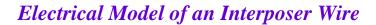

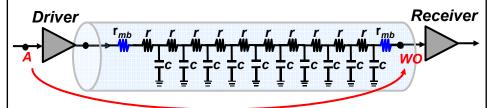

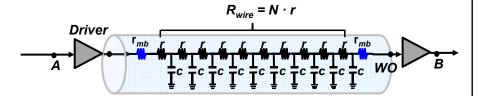

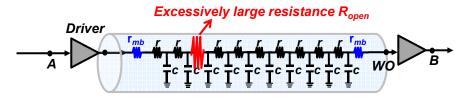

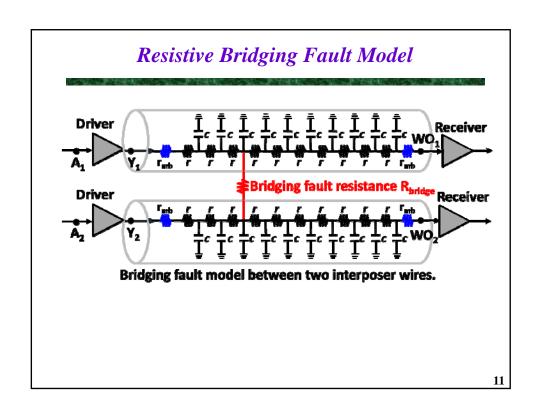

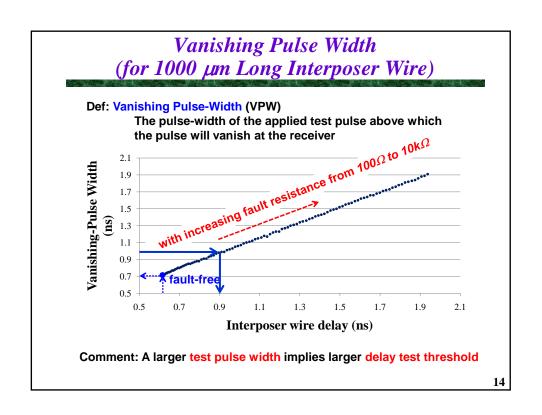

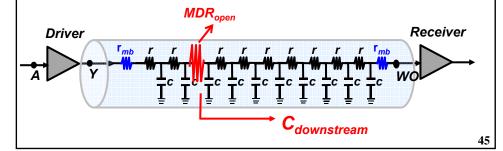

An interposer wire is decomposed into multiple segments of r and c  $r_{mb}$  is the resistance of the micro-bump

'IW-delay': interposer wire delay from A to WO

9

# Resistive Open Fault Model

(a) Fault-free model of an interconnect.

(b) Faulty model of an interconnect with a resistive open fault.

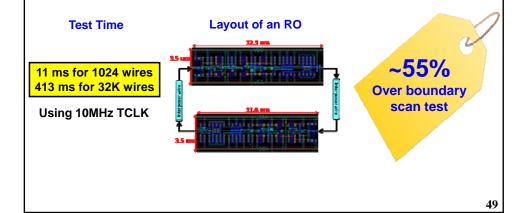

# Test Time

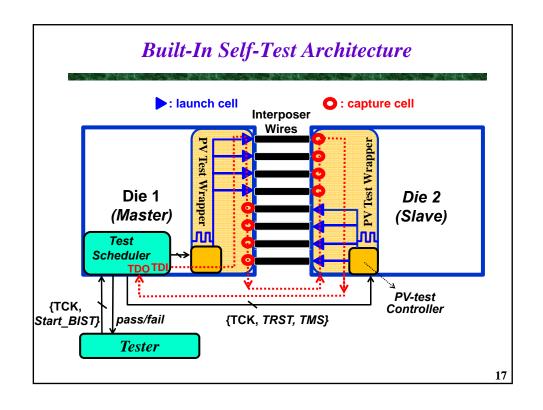

◆ A PV-test session using 10MHz test clock is about 0.82 ms for 1024 interposer wires 26.21 ms for 32K (32,768) interposer wires

### Area Overhead

#### Estimation is based on a 90nm CMOS process

| Area overhead             |                                   |                     |  |  |

|---------------------------|-----------------------------------|---------------------|--|--|

| Type                      | Cell Name                         | Layout Area (μm*μm) |  |  |

| Basic<br>Cells            | INVERTER                          | 2.82                |  |  |

|                           | 2-input NAND Cell                 | 2.94                |  |  |

|                           | MUX Cell                          | 8.47                |  |  |

|                           | FF Cell                           | 17.64               |  |  |

| Basic<br>Macros           | <b>Boundary Scan Cell</b>         | 52.22               |  |  |

|                           | Launch Cell                       | 92.56               |  |  |

|                           | Capture Cell                      | 69.16               |  |  |

|                           | PV-test controller                | 670.3               |  |  |

| Overhead                  | 55.55% for 1024 interposer wires  |                     |  |  |

| Percentage<br>Over 1149.1 | 54.9% for 32,768 interposer wires |                     |  |  |

21

## Summary of PV-Test

The interposer needs to be tested alone and thoroughly. And also, when a 2.5-D IC fails,

We know if the interposer should be responsible.

#### Advantages of Pulse-Vanishing Test

- Simple fault detection scheme (No post-processing)

- Delay Test without die-to-die high-speed clock synchronization

- Boundary-Scan-Like Test Architecture (55.55% overhead)

- On-the-spot Diagnosis (good for future self-repair)

#### **Outline**

- **♦** Introduction

- **♦** Pulse-Vanishing Test (PV-Test)

- **→ VOT-Based Oscillation Test**

- Characterization-based parametric fault testing

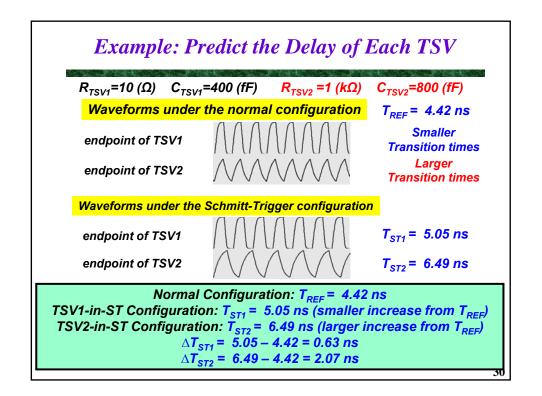

# Brief Summary of our Idea

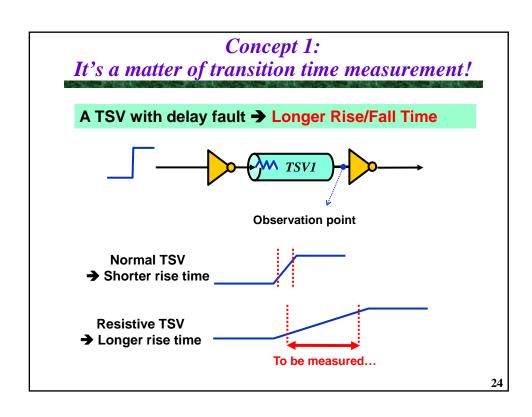

## TSV Delay → Transition Time

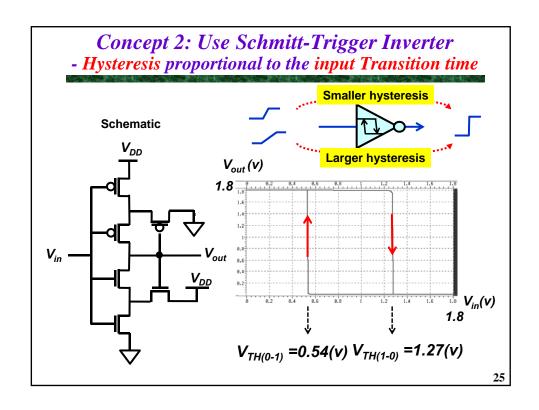

# Transition Time → Oscillation Period Change

(from normal to Schmitt-Trigger)

(Easily Measurable)

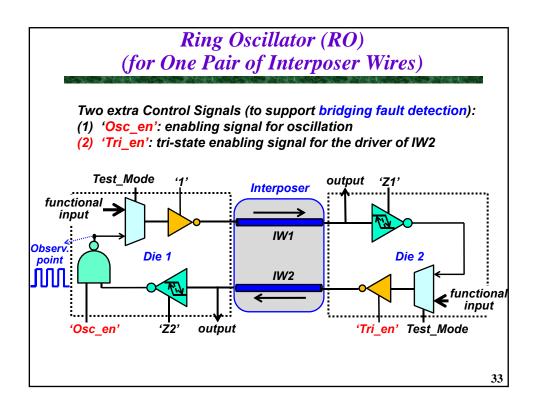

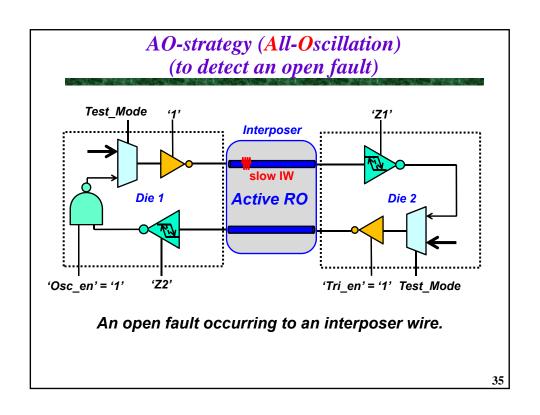

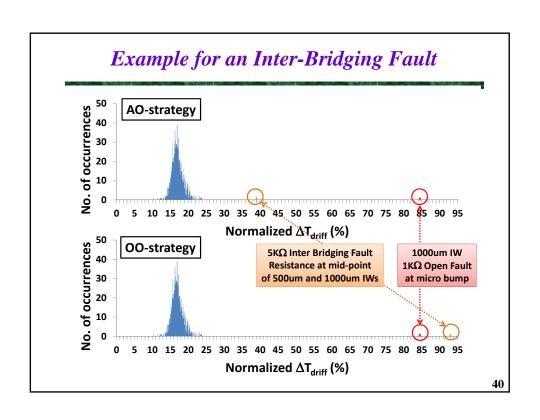

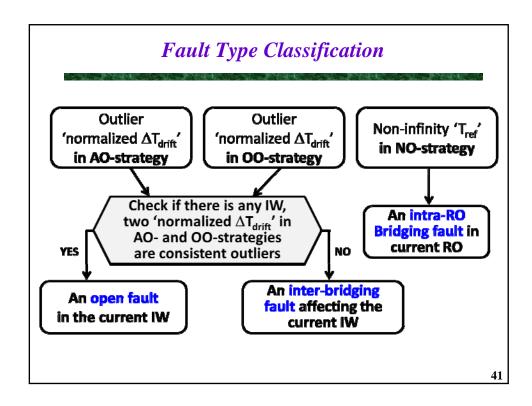

| Three Test Strategies                                                                                                                                                                                                               |                                  |                                           |                                                                                         |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

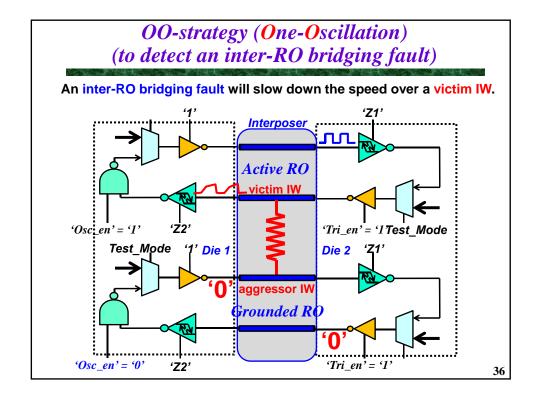

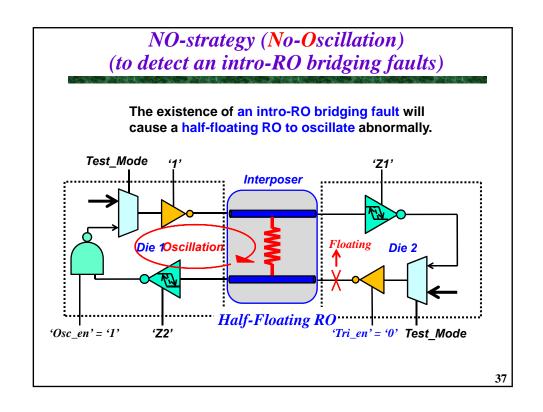

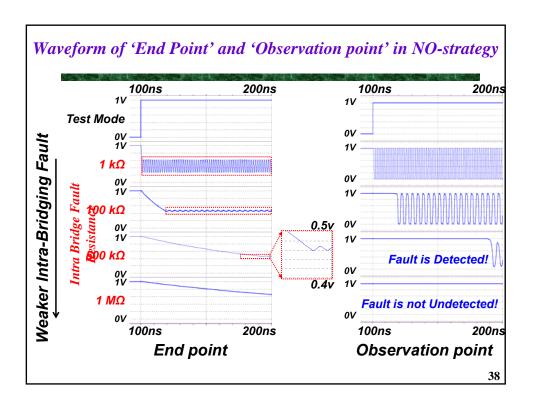

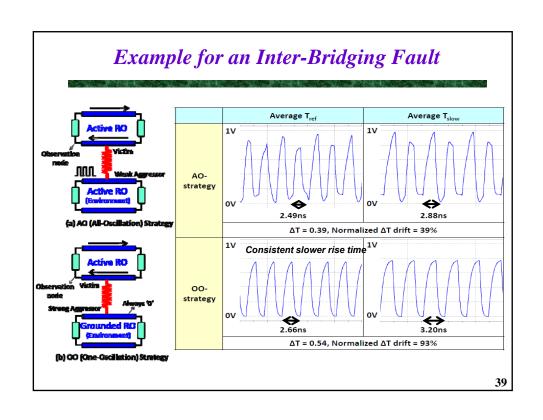

| Principles: (1) All ROs oscillate concurrently to detect "resistive open faults" (2) One RO oscillates at a time to detect "inter-RO resistive bridging faults" (3) No RO oscillates to detect "intra-RO resistive bridging faults" |                                  |                                           |                                                                                         |  |  |

|                                                                                                                                                                                                                                     | Test Strategy                    | RO Settings                               | Test Actions                                                                            |  |  |

| Test<br>OPEN                                                                                                                                                                                                                        | AO-strategy<br>(All Oscillation) | Every RO is Active                        | Measure {T <sub>REF</sub> ,T <sub>ST1</sub> ,T <sub>ST2</sub> } of every RO in sequence |  |  |

| Test<br>Inter-RO<br>BRIDGING                                                                                                                                                                                                        | OO-strategy<br>(One Oscillation) | Target RO is Active<br>(One RO at a time) | Measure<br>{T <sub>REF</sub> ,T <sub>ST1</sub> ,T <sub>ST2</sub> }<br>of the target RO  |  |  |

|                                                                                                                                                                                                                                     |                                  | The others are<br>Grounded                | NA                                                                                      |  |  |

| Test<br>Intro-RO<br>BRIDGING                                                                                                                                                                                                        | NO-strategy<br>(No Oscillation)  | Every RO is Half-<br>Floating             | Measure {T <sub>REF</sub> } of every RO                                                 |  |  |

| 34                                                                                                                                                                                                                                  |                                  |                                           |                                                                                         |  |  |

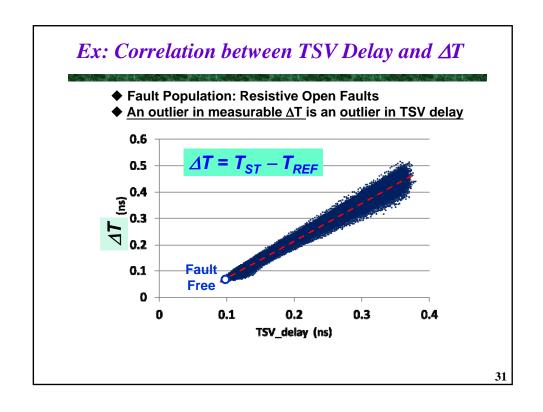

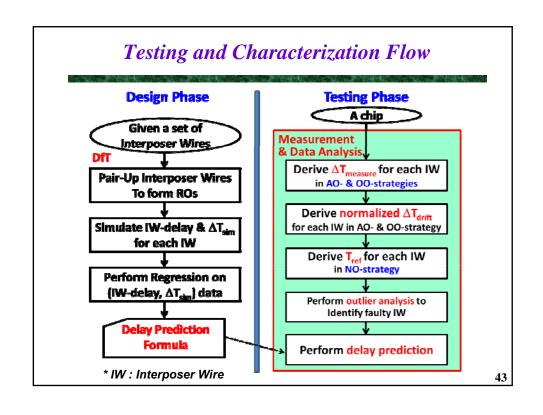

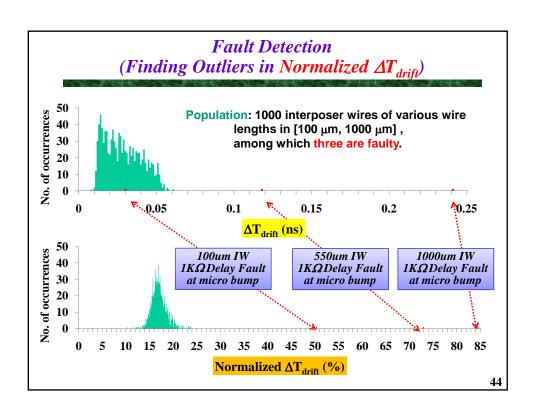

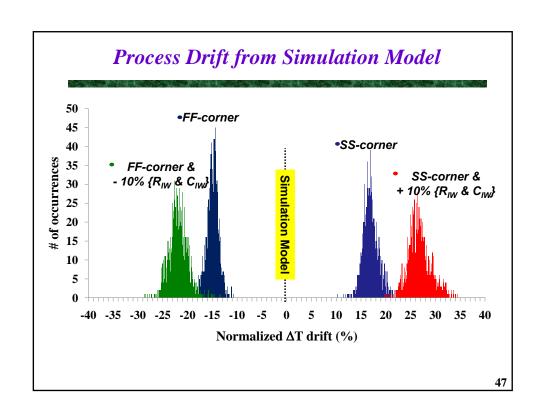

# Normalized $\Delta T_{drift}$ for Outlier Analysis

For each IW  $w_i$ , we have two versions of  $\Delta T$ :

$$\Delta T_{sim}(w_i) = T_{ST\_sim}(w_i) - T_{REF\_sim}(w_i)$$

$$\Delta T_{measure}(w_i) = T_{ST\_measure}(w_i) - T_{REF\_measure}(w_i)$$

$\Delta T_{drift}(w_i)$  respresents the drifting amount of a measurement version of  $\Delta T$  away from its simulation version:

$$\Delta T_{drift}(w_i) = \Delta T_{measure}(w_i) - \Delta T_{sim}(w_i)$$

To take into account of the wire-length diversity, we further normalize it:

$$(Normalized \Delta T_{drift}) = \left(\frac{\Delta T_{measure} - \Delta T_{sim}}{\Delta T_{sim}}\right) \cdot 100\%$$

# Fault Detection Capability (For Resistive Open Faults)

MDR<sub>open</sub>: Minimum Detectable Open Fault Resistance

This metric refers to the open fault resistance value beyond which the proposed test method can detect the fault successfully based on the outlier analysis using  $3\sigma$  rule.

# Detectable Extra-RC: (MDR<sub>open</sub>) \* (C<sub>downstream</sub>) 50.7 ps

# Resistive Open Fault Detection Capability

A resistive open fault occurring at the micro-bump of the driver side of a 1000um long interposer wire.

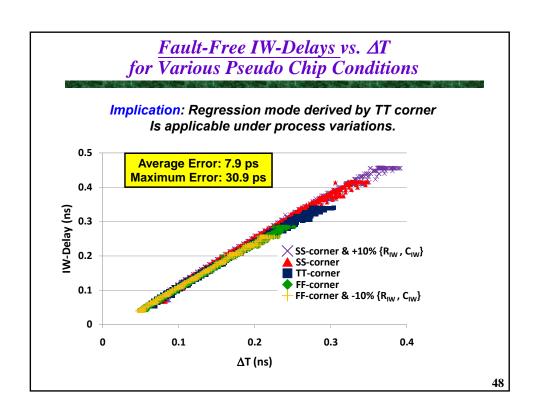

| Pseudo<br>Chip Conditions | MDR <sub>open</sub><br>(Min. Detectable Open<br>Fault Resistance) | Detectable<br>Extra-RC |

|---------------------------|-------------------------------------------------------------------|------------------------|

| #1 (FF & -10% RC)         | 245 Ω                                                             | 50.7 ps                |

| #2 (FF)                   | 76 Ω                                                              | 17.5 ps                |

| #3 (SS)                   | 113 Ω                                                             | 26.0 ps                |

| #4 (SS & +10% RC)         | 78 Ω                                                              | 19.7 ps                |

| Average                   | 145 Ω                                                             | 31.4 ps                |

# Summary of VOT-Based Oscillation Test

The interposer needs to be tested alone and thoroughly. And also, when a 2.5-D IC fails,

We know if the interposer should be responsible.

#### **Conclusion**

| Criterion                 | PV-test                                                           | VOT-based oscillation test                    |

|---------------------------|-------------------------------------------------------------------|-----------------------------------------------|

| Basic Concept             | Check if pulse will vanish                                        | Measure ΔT                                    |

| Fault Detection<br>Scheme | Test threshold based                                              | Outlier analysis                              |

| Area overhead             | 55.5% over IEEE-1149.1                                            | 55.7% over IEEE-1149.1                        |

| Test time                 | <u>0.82</u> ms for 1024 wires<br><u>26.21</u> ms for 32K wires    | 4.7 ms for 1024 wires<br>177 ms for 32K wires |

| Other benefits            | No post-processing<br>On-the-spot diagnosis<br>Easier self-repair | Delay characterization<br>Process tracking    |

Outlier analysis: A measurement sample that significantly deviates away from the entire population indicates a fault