## Contact engineering of GaN-on-silicon power devices for breakdown voltage enhancement

This article has been downloaded from IOPscience. Please scroll down to see the full text article.

2013 *Semicond. Sci. Technol.* 28 074018

(<http://iopscience.iop.org/0268-1242/28/7/074018>)

[View the table of contents for this issue](#), or go to the [journal homepage](#) for more

Download details:

IP Address: 140.114.21.200

The article was downloaded on 23/08/2013 at 04:18

Please note that [terms and conditions apply](#).

## INVITED PAPER

# Contact engineering of GaN-on-silicon power devices for breakdown voltage enhancement

Yu-Syuan Lin, Yi-Wei Lian, Jui-Ming Yang, Hou-Cheng Lu,

Yen-Chieh Huang, Chih-Hsuan Cheng and Shawn S H Hsu<sup>1</sup>

Department of Electrical Engineering, National Tsing Hua University, Hsinchu, Taiwan

E-mail: [shhsu@ee.nthu.edu.tw](mailto:shhsu@ee.nthu.edu.tw)

Received 3 December 2012, in final form 1 February 2013

Published 21 June 2013

Online at [stacks.iop.org/SST/28/074018](http://stacks.iop.org/SST/28/074018)

## Abstract

Two contact engineering approaches are proposed and investigated to enhance the breakdown voltage  $V_{BK}$  in GaN-on-Si power devices, including the hybrid Schottky–ohmic-drain structure for AlGaN/GaN HEMTs and the selective Si-diffusion structure for AlGaN/GaN SBDs. With the hybrid Schottky–ohmic drain, the devices showed a zero onset voltage and reduced off-state leakage current by one order of magnitude, compared with that of the traditional ohmic-drain devices. The breakdown voltage was also enhanced with comparable on-resistance. For the SBDs with the selective silicon-diffusion layer underneath ohmic metal at the cathode, a low-contact resistance  $R_c$  of  $0.2 \Omega \text{ mm}$  and a smooth ohmic metal morphology were obtained. The SBDs with the additional silicon diffusion layer showed enhanced  $V_{BK}$ , compared with that of the conventional SBDs. The results demonstrate that the proposed contact engineering approaches are useful for the breakdown voltage enhancement of GaN-on-Si power devices.

(Some figures may appear in colour only in the online journal)

## 1. Introduction

GaN-based power devices such as high electron mobility transistors (HEMTs) and Schottky barrier diodes (SBDs) are promising for next generation power electronic applications due to their superior electrical properties, as evident from the excellent Baliga's figure-of-merit (BFOM, defined as  $V_{BK}^2/R_{on,sp}$ , where  $V_{BK}$  is the breakdown voltage and  $R_{on,sp}$  is the specific on-resistance) [1]. Also, the growth of the high-quality GaN epitaxial layer on a large-scale silicon substrate has shown substantial progress in recent years, which allows the production of GaN-based devices taking advantage of modern silicon technology with low cost. Recent advances have demonstrated high-performance GaN-based power devices realized on the silicon substrate, while the  $V_{BK}$  of these devices are still below the theoretical limit of GaN [2–5] and could further be improved. It has been reported

that the off-state breakdown voltages of these devices are often limited by 'vertical breakdown' due to the rapid increase of the buffer leakage current [6]. The buffer leakage current could cause additional energy loss and reduce the system efficiency.

For the breakdown voltage enhancement and off-state leakage current suppression of the GaN power devices, the growth of a high-quality buffer layer plays an important role. The usage of the ultra-thick buffer layer [2], carbon (C) or iron (Fe)-doped high-resistive buffer layer [7, 8] and AlGaN back-barrier [9] was proposed. In addition, the Si substrate removal and wafer transfer technique were employed to eliminate the leakage path through the buffer layer in GaN HEMTs [3]. It has also been reported that the ohmic contact process is critical to the device buffer leakage and breakdown voltage [10], which probably can be attributed to the deep alloy spikes formed in the GaN channel and/or buffer layer during high-temperature annealing of the ohmic process. These metal spikes underneath the ohmic contact cause undesired high electric-field (e-field) peaks at the sharp points of the spikes inducing extra buffer

<sup>1</sup> Author to whom any correspondence should be addressed.

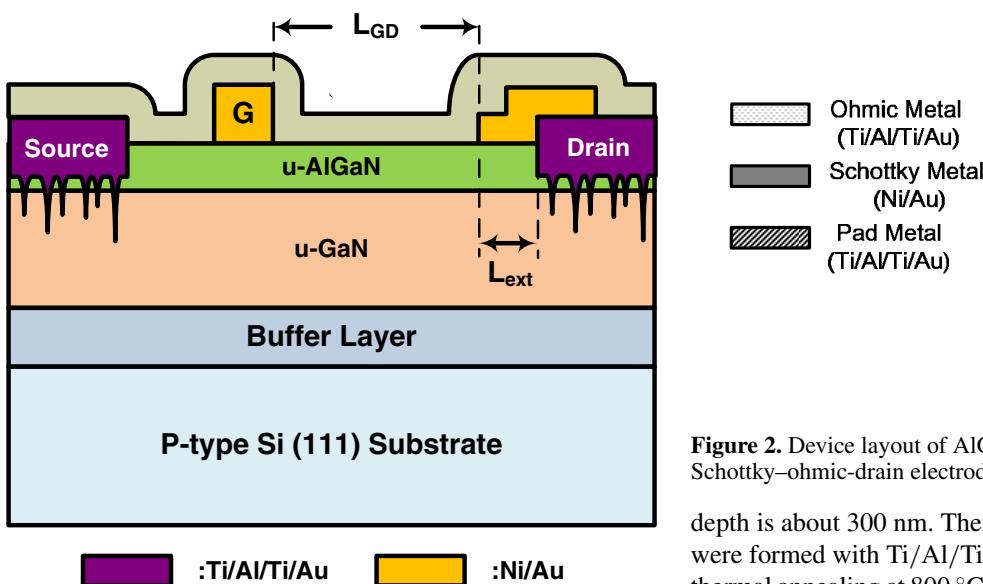

**Figure 1.** Device structure of AlGaN/GaN HEMTs on the silicon substrate with hybrid Schottky-ohmic-drain electrode.

leakage current. The Schottky-drain structure was proposed to avoid the premature breakdown associated with the alloy spikes [11]. By replacing the alloy-type ohmic contact with a Schottky metal of relatively smooth contact interface, the breakdown voltage is improved, while the onset voltage is also increased to be  $\sim 1$  V.

In this paper, two different contact engineering approaches are proposed to enhance the breakdown voltage in GaN-on-Si power devices. First, the hybrid Schottky-ohmic-drain electrode is employed for AlGaN/GaN HEMTs, which demonstrates the enhanced off-state characteristic without degradation of the current level and on-resistance ( $R_{on}$ ). With a Schottky metal extension over the drain ohmic contact, the hybrid-drain structure can effectively alleviate the concentration of the e-field line around the alloy spikes at the drain side, resulting in the reduced leakage current and improved breakdown voltage. In addition, we propose a selective Si-diffusion approach for the AlGaN/GaN SBDs to alleviate the alloy spiking at the cathode. A smoother ohmic metal morphology can be obtained and the e-field peaks in the vicinity of the ohmic contact can be reduced. With the Si-diffusion layer applied to the cathode side, the devices achieve improved  $V_{BK}$  and low-contact resistance  $R_c$  simultaneously, compared with the conventional AlGaN/GaN SBDs.

## 2. Devices design and fabrication

### 2.1. Hybrid-drain AlGaN/GaN HEMTs

Figure 1 shows the cross section of the AlGaN/GaN HEMT with the proposed hybrid Schottky-ohmic-drain electrode. The layer structure of the AlGaN/GaN HEMT consists of a 1  $\mu$ m unintentionally doped layer (including the buffer and GaN channel layer) and followed by a 24 nm thick undoped  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  barrier layer. Device isolation was achieved by dry etching using the  $\text{Cl}_2/\text{Ar}$  gas mixture and the etching

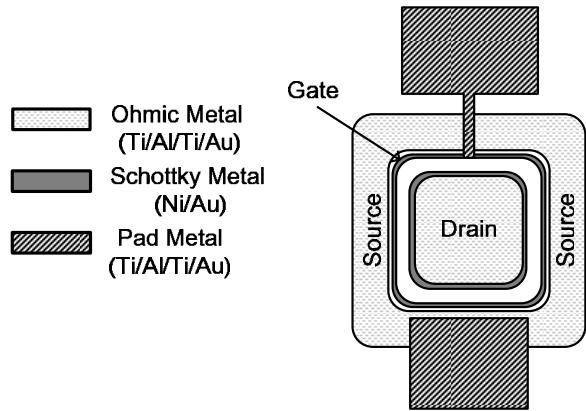

**Figure 2.** Device layout of AlGaN/GaN HEMTs with the hybrid Schottky-ohmic-drain electrode.

depth is about 300 nm. Then the source/drain ohmic contacts were formed with Ti/Al/Ti/Au (20/150/45/55 nm) by rapid thermal annealing at 800  $^{\circ}\text{C}$  for 30 s in a  $\text{N}_2$  ambient. Note that the ohmic recess process with low-power Ar plasma etching was adapted to reduce the ohmic contact resistance before the deposition of the ohmic metals. With a very low RF power and only a short period of time (5 W, 1 min), the ohmic recess depth is very shallow (should be in the order of several nanometers). After the ohmic contact process, the Ni/Au contact (20 nm/300 nm) was deposited to form the Schottky gate by the lift-off process, and the same gate Schottky metal is also utilized for the Schottky- and hybrid-drain devices. A silicon nitride/silicon dioxide/silicon nitride layer using plasma-enhanced chemical vapor deposition (PECVD) was then deposited as the surface passivation layer.

As shown in figure 1, the Schottky metal of the proposed hybrid-drain structures is deposited above the alloyed ohmic metal directly with different extension length  $L_{ext}$ . It should be emphasized that no additional photomasks and extra process steps are required, because the hybrid drain can be formed simultaneously with the Schottky gate electrode. Figure 2 illustrates the device layout and the details of the metal used in different electrodes. In our previous studies [12, 13], we have concluded that the dry etching damage at the mesa edge during the mesa isolation process could be an important factor to degrade the leakage current and the breakdown voltage of the GaN-based devices. The square-gate layout approach is employed to alleviate the effects of traps at the mesa edge on transistor characteristics in this study [13]. Note that mesa isolation is not needed for the close-type layout of individual devices. However, the mesa process is essential in general integrated circuit applications for the device isolation.

### 2.2. Selective silicon-diffused AlGaN/GaN SBDs

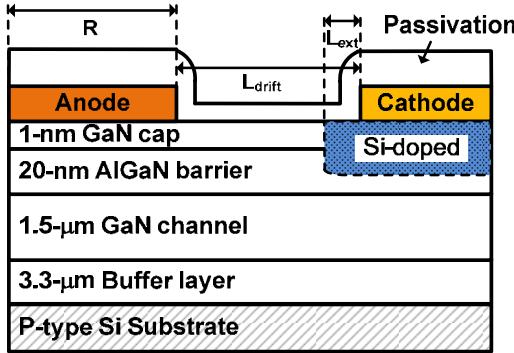

Figure 3 shows the cross section of the proposed AlGaN/GaN SBDs on the Si substrate with the selective silicon-diffusion design. The Si-diffusion process is employed in the cathode region before the ohmic contact process. With a circular layout,  $R$  is the radius of the Schottky electrode and  $L_{ext}$  is the extended length of the Si-diffused region over the ohmic metal edge. The epi-structure consists of a 3.3  $\mu$ m buffer layer, a 1.5  $\mu$ m GaN channel layer, followed by a 20 nm  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{N}$  barrier

**Figure 3.** Device structure of the proposed selective Si-diffused AlGaN/GaN SBD on the silicon substrate.

layer and a 1 nm GaN cap layer on top. The length of  $L_{\text{ext}}$  is 1  $\mu\text{m}$  in the devices. The typical photolithography method was employed to define  $L_{\text{ext}}$  and the optical microscope inspection was used to verify the misalignment, which is within  $\sim 0.2 \mu\text{m}$ . Considering the effect of lateral Si out-diffusion, a SiO layer was applied on top of the Si-dopant layer before the diffusion process to minimize the lateral diffusion. With the diffusion depth of Si  $\sim 10 \text{ nm}$ , the lateral diffusion should also be in the nm range, which could be neglected. The mesa isolation was accomplished by inductive couple plasma using  $\text{Cl}_2/\text{Ar}$  mixture gas, and the etching depth is about 300 nm. After defining the selective diffusion region by a photoresist, a 50 nm Si layer was deposited as a dopant source using the electron beam evaporation. After lift-off, a 150 nm  $\text{SiO}_2$  layer was encapsulated by PECVD at 300  $^{\circ}\text{C}$  to prevent the surface dissociation during the succeeding high-temperature diffusion process [14]. The Si-diffusion process was then performed at 1000  $^{\circ}\text{C}$  for 30 min in  $\text{N}_2$  ambient. After the removal of the  $\text{SiO}_2$  cap layer and the remaining silicon, the ohmic contacts were formed with Ti/Al/Ni/Au using e-beam evaporation and followed by rapid thermal annealing at 850  $^{\circ}\text{C}$  for 30 s. The metal stack of Ni/Au (30/270 nm) was then deposited to form the Schottky contact. A similar layer structure with that in the GaN HEMT process is used for surface passivation.

### 3. Results and discussion

#### 3.1. Hybrid-drain AlGaN/GaN HEMTs

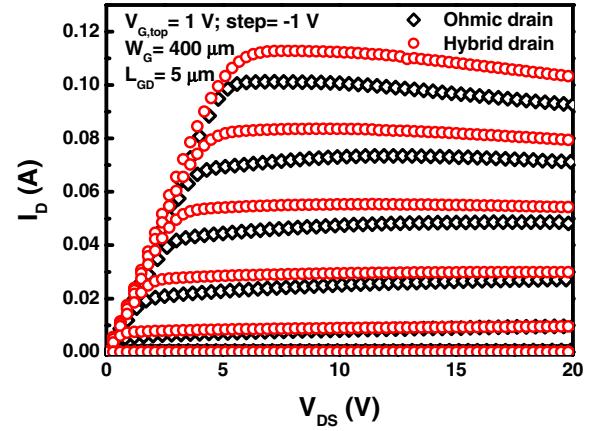

The fabricated devices have the gate length ( $L_G$ ) and gate-source spacing ( $L_{GS}$ ) both of 2  $\mu\text{m}$  and a total gate width of 400  $\mu\text{m}$ . All the devices are in depletion mode with a similar threshold voltage. The ( $I$ - $V$ ) characteristics of the conventional and hybrid-drain devices are compared in figure 4, both with a gate-drain spacing  $L_{GD}$  of 5  $\mu\text{m}$ . As can be seen, the onset voltage of the hybrid-drain devices is almost zero, similar with the conventional pure ohmic-drain devices. When the drain voltage  $V_{DS}$  is smaller than the turn-on voltage of the Schottky contact, the Schottky portion of the contact is still off and all the current flows only via the ohmic part of the drain electrode. As  $V_{DS}$  increases up to  $\sim 1 \text{ V}$ , the Schottky electrode starts to turn on, providing an additional current conduction path, and the equivalent drain contact resistance becomes smaller. Consequently, comparable  $R_{\text{on}}$  and similar

**Figure 4.** ( $I$ - $V$ ) characteristics of AlGaN/GaN HEMTs with the conventional ohmic drain and the proposed hybrid drain.

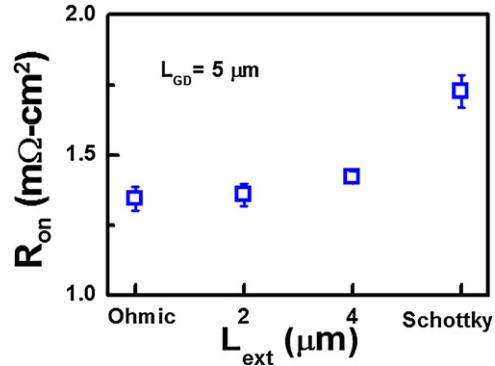

**Figure 5.**  $R_{\text{on}}$  with different  $L_{\text{ext}}$  of hybrid-drain devices compared with both pure ohmic and Schottky-drain devices.

or even higher drain current density can be achieved. Note that the Schottky electrode at the drain side provides an auxiliary current path at high drain voltages, which reduces the equivalent contact resistance. Also, the extended Schottky electrode redistributes the e-field around the drain side. Both factors may affect the carrier saturation velocity, leading to an increased saturation current. The exact physics behind the observed characteristics is still not fully understood, which needs to be further investigated.

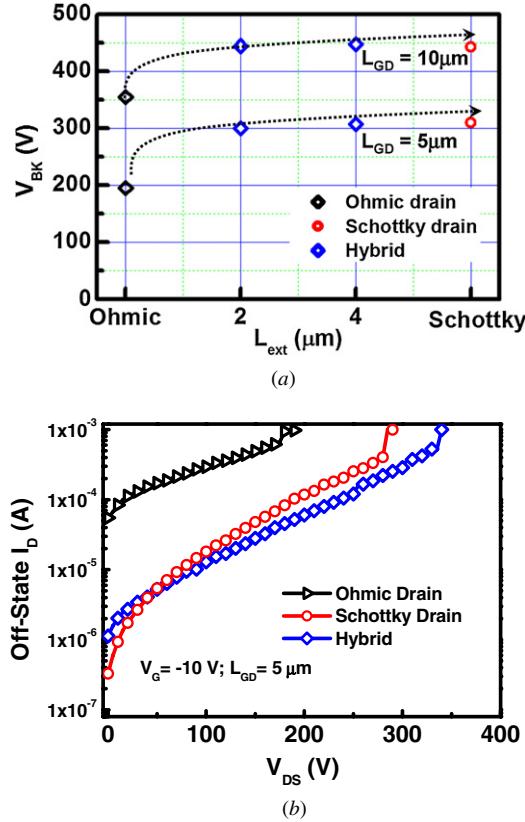

Figure 5 compares  $R_{\text{on}}$  (average from five typical transistors) of devices with both pure ohmic and Schottky drains, and also the hybrid-drain devices with  $L_{\text{ext}}$  of 2 and 4  $\mu\text{m}$  ( $L_{GD}$  of 5  $\mu\text{m}$  is kept constant). With a relatively small  $L_{\text{ext}}$  of 2  $\mu\text{m}$ ,  $R_{\text{on}}$  of the hybrid-drain devices (1.35  $\text{m}\Omega \text{ cm}^2$ ) is almost identical to that of the conventional ohmic-drain devices (1.34  $\text{m}\Omega \text{ cm}^2$ ). Also, it can be observed that  $R_{\text{on}}$  increases with  $L_{\text{ext}}$  from the ohmic-drain devices (equivalent  $L_{\text{ext}} = 0$ ) toward the pure Schottky-drain devices (1.72  $\text{m}\Omega \text{ cm}^2$ ). Figure 6(a) shows the corresponding off-state breakdown voltage of each type of devices with  $L_{GD} = 5$  and 10  $\mu\text{m}$ , respectively. Both the Schottky- and hybrid-drain HEMTs present higher breakdown voltage compared with that in the ohmic-drain devices. It should be mentioned that the hybrid-drain devices show even smaller leakage current at a high drain bias, as shown in figure 6(b). The main reason is that the combination of ohmic and Schottky contact acts

**Figure 6.** (a) Off-state breakdown characteristics of pure ohmic- and Schottky-drain devices, and hybrid-drain devices with  $L_{ext}$  of 2 and 4  $\mu\text{m}$ , (b) Off-state leakage characteristics of three different types of devices ( $L_{ext} = 2\mu\text{m}$  of hybrid-drain device).

like a  $\Gamma$ -shape field plate, which is efficient for lowering the peak of the e-field at the drain side. In addition, the extended Schottky contact also provides a shallow depletion region underneath, which functions similarly to the floating metal ring in the traditional SiC-based power rectifiers for the e-field redistribution and reduction of the peak e-field [15]. The results of both figures 5 and 6 suggest that the hybrid-drain devices with  $L_{ext} = 2\mu\text{m}$  are about optimal for achieving the high breakdown voltage compared with the Schottky-drain devices, while also without the degradation of  $R_{on}$  in contrast with the traditional ohmic-drain devices.

### 3.2. Selective silicon-diffused AlGaN/GaN SBDs

The TLM patterns with the Si-diffusion layer are designed and fabricated to observe the doping effect and optimize the processing condition of the Si-diffusion layer. The ohmic contact with a very low  $R_c$  of 0.2  $\Omega\text{ mm}$  and specific contact resistance  $\rho_{c,sp}$  of 0.86  $\mu\Omega\text{ cm}^2$  can be achieved under 1000  $^{\circ}\text{C}$  and 30 min in  $\text{N}_2$  ambient. The reduced sheet resistance is also obtained with the Si-diffusion layer (462  $\Omega/\square$ ), compared with the TLM pattern (528  $\Omega/\square$ ) in the conventional design.

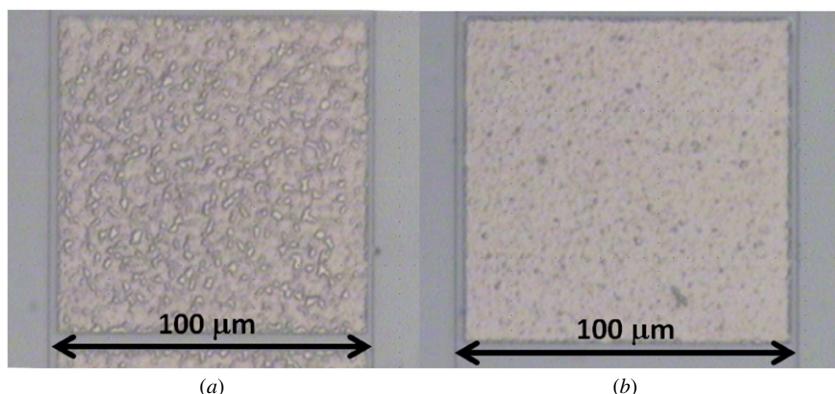

Figures 7(a) and (b) show the top-view micrographs of the TLM pattern without and with the silicon diffusion layer, respectively. The much improved surface morphology with the silicon diffusion layer can be clearly observed. Although not shown here, the TLM patterns were also measured by atomic force microscope. The mean roughness  $\text{Ra}$  of 22.3/55.1 nm and RMS roughness  $\text{Rq}$  of 29.5/69.4 nm are obtained from Si-doped and undoped TLM, respectively, which agree very well with the trend observed from the optical microscope, as shown in figure 7. The results indicate that the additional Si-diffusion layer underneath the ohmic contact can suppress the alloy spike formation during high-temperature annealing. It should be noted that the improvement of the surface morphology and contact resistance can also be achieved by using the Nb or Ta in the ohmic contact alloying process [16, 17].

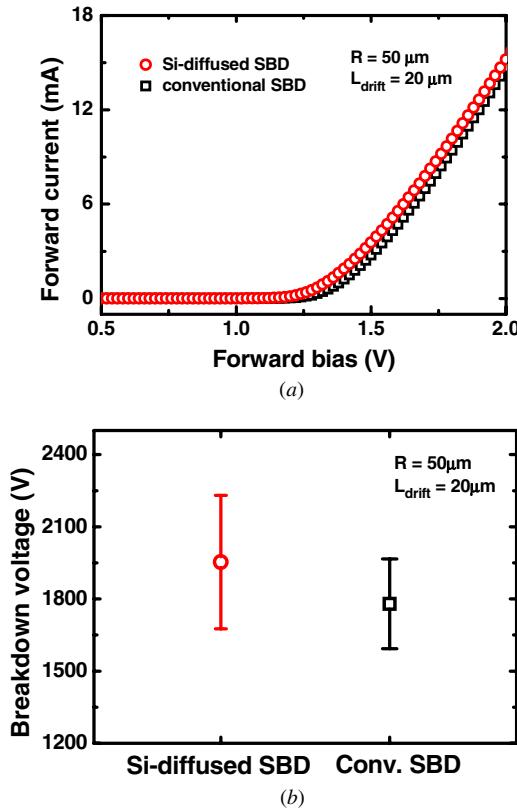

Figure 8(a) shows the forward ( $I$ - $V$ ) characteristics of both the conventional and proposed Si-diffused GaN SBDs on Si with an  $L_{drift}$  of 20  $\mu\text{m}$ . The ( $I$ - $V$ ) characteristics are similar with a typical onset voltage of  $\sim 1.4\text{ V}$ . Figure 8(b) shows the measured  $V_{BK}$  of the SBDs (average from three typical devices). The proposed SBDs show a higher average  $V_{BK}$  of 1900 V, compared with that of 1780 V for the conventional SBDs. This can be attributed to the extended Si-doped region underneath the ohmic contact, which suppresses the alloy spiking effect and alleviates the high e-field peaks around the spikes.

It should be emphasized that we focus on investigating the effect of the Si-diffusion layer on alloyed-type ohmic contact in this work, and the rest of the processing steps are kept identical with our previous studies for a well-controlled experiment. In theory, a non-alloyed process should also provide good ohmic contact if with the Si-doped layer. Based on the literature survey, the non-alloyed ohmic contact

**Figure 7.** Surface morphology micrographs of the ohmic metal in TLM pattern ( $100 \times 100\mu\text{m}^2$ ) (a) without and (b) with the Si-diffusion layer.

**Figure 8.** Comparison of conventional and the proposed silicon-diffused SBDs (a) forward ( $I$ – $V$ ) characteristics, (b) breakdown voltage.

(Ti/Al based) fabricated on heavily doped n-type AlGaN barrier layer exhibits a contact resistance of  $0.96\ \Omega\text{ mm}$  and a sheet resistance of  $383\ \Omega/\square$  by Si ion implantation, while the alloyed ohmic contact shows the contact resistance of  $0.46\ \Omega\text{ mm}$  and sheet resistance of  $344\ \Omega/\square$ , respectively [18]. Also, it has been reported that a low specific contact resistivity of  $1.2 \times 10^{-6}\ \mu\Omega\text{ cm}^2$  can be obtained for Ti/Al-based non-alloyed ohmic contact formation with a Si-diffusion method at a relative low annealing temperature of  $550\text{ }^\circ\text{C}$  for AlGaN/GaN heterostructures [19].

Finally, although this study assumes the formation of spikes in the alloyed-type ohmic contact, it should be mentioned that the alloy spikes of ohmic contact with random distribution could not be always observed for AlGaN/GaN heterostructures [20]. Also, the ohmic contact formation mechanisms are still under discussion [21]. More in-depth material characterization is needed for this issue.

#### 4. Conclusion

In this paper, we proposed a hybrid Schottky–ohmic-drain structure for AlGaN/GaN HEMTs and a selective Si-diffusion design for AlGaN/GaN SBDs on the silicon substrate, both for off-state breakdown characteristics enhancement of GaN-on-Si power devices. For the hybrid-drain HEMTs, the Schottky metal extension formed a  $\Gamma$ -shaped electrode, reducing the peak electric field and smoothing the electric field distribution around the drain. The hybrid-drain design also provided an extra current path to lower the on-resistance. The measured results showed a zero onset voltage and reduced off-state

leakage current by one order of magnitude compared with that of the traditional ohmic-drain devices. The breakdown voltage was also enhanced without any degradation of the on-resistance. Also, with the selective silicon-diffusion layer underneath the ohmic contact, a low-contact resistance of  $0.2\ \Omega\text{ mm}$  and smooth ohmic metal morphology were obtained. The AlGaN/GaN Schottky barrier diodes with the additional silicon diffusion layer showed enhanced  $V_{BK}$ , compared with that of the conventional SBDs. The results demonstrated that both approaches are effective solutions to alleviate the effect of localized metal spiking beneath the ohmic contact for the breakdown voltage enhancement in GaN-on-silicon power devices.

#### References

- [1] Baliga B J 1995 *Power Semiconductor Devices* (Boston, MA: PWS Publishing Co.) p 417

- [2] Rowena I B, Selvaraj S L and Egawa T 2011 *IEEE Trans. Electron Devices* **58** 1534

- [3] Srivastava P *et al* 2010 *IEEE Electron Device Lett.* **31** 851

- [4] Tom'as A, Fontserè A, Placidi M, Baron N, Chenot S, Moreno J C and Cordier Y 2012 *Semicond. Sci. Technol.* **27** 125010

- [5] Lachab M, Sultana M, Fatima H, Adivarahan V, Fareed Q and Khan M A 2012 *Semicond. Sci. Technol.* **27** 125001

- [6] Zhou C, Jiang Q, Huang S and Chen K J 2012 *IPSD'12: 24th IEEE Int. Symp. on Power Semiconductor Devices and ICs* p 245

- [7] Choi Y C, Pophristic M, Peres B, Cha H Y, Spencer M G and Eastman L F 2007 *Semicond. Sci. Technol.* **22** 517

- [8] Choi Y C, Pophristic M, Cha H Y, Peres B, Spencer M G and Eastman L F 2006 *IEEE Trans. Electron Devices* **53** 2926

- [9] Visalli D, Hove M V, Derluyn J, Degroote S, Leys M, Chang K, Germain M and Borghs G 2009 *Japan. J. Appl. Phys.* **48** 04C101

- [10] Dora Y, Chakraborty A, Heikman S, McCarthy L, Keller S, DenBaars S P and Mishra U K 2006 *IEEE Electron Device Lett.* **27** 529

- [11] Lu B, Piner E L and Palacios T 2010 *IEEE Electron Device Lett.* **31** 302

- [12] Lin Y S, Lian Y W and Hsu S H 2010 *IEEE Electron Device Lett.* **31** 102

- [13] Lin Y S, Wu J Y, Chan C Y, Hsu S H, Huang C F and Lee T C 2009 *IEEE Trans. Electron Devices* **56** 3207

- [14] Hashizume T and Hasegawa H 2004 *Appl. Surf. Sci.* **234** 387

- [15] Bhatnagar M, Nakanishi H, Bothra S, McLarty P K and Baliga B J 1993 *IPSD'93: Proc. 5th Int. Symp. on Power Semiconductor Devices and ICs* (Monterey, CA, 18–20 May) p 89

- [16] Vanko G, Lalinský T, Mozolová Ž, Liday J, Vogrinčík P, Vincze A, Uherek F, Haščík Š and Kostič I 2008 *Vacuum* **82** 193

- [17] Kim K H, Jeon C M, Oh S H, Lee J-L, Park C G, Lee J H, Lee K S and Koo Y M 2005 *J. Vac. Sci. Technol. B* **23** 322

- [18] Recht F, McCarthy L, Rajan S, Chakraborty A, Poblenz C, Corrion A, Speck J S and Mishra U K 2006 *IEEE Electron Device Lett.* **27** 205

- [19] Murata T, Hikita M, Ishida H, Hirose Y, Inoue K, Uemoto Y and Tanaka T 2004 *Intl Meeting for Future of Electron Devices* p 47

- [20] Roccaforte F, Iucolano F, Alberti A, Giannazzo F, Puglisi V, Bongiorno C, Franco S D and Raineri V 2006 *Superlatt. Microstruct.* **40** 373

- [21] Tokuda H, Kojima T and Kuzuhara M 2012 *Appl. Phys. Lett.* **101** 262104