# An Ultra-Low-Power 24 GHz Low-Noise Amplifier Using 0.13 $\mu$ m CMOS Technology

Wei-Han Cho and Shawn S. H. Hsu, *Member, IEEE*

**Abstract**—This study presents an ultra-low-power 24 GHz low-noise amplifier (LNA) using 0.13  $\mu$ m CMOS technology. We propose of using the minimum noise measure ( $M_{\text{MIN}}$ ) as the guideline to determine the optimal bias and geometry of the transistors in the circuit. The power-constrained simultaneous noise and input matching (PCSNIM) technique is also employed for this design. With the proposed design approach, the LNA achieves a peak gain of 9.2 dB and a minimum *NF* of 3.7 dB under a supply voltage of 1 V. The associated power consumption is only 2.78 mW.

**Index Terms**—CMOS, k-band, low-noise amplifier (LNA), low power.

## I. INTRODUCTION

CONTINUOUS scaling of CMOS technology keeps driving the innovation of RFICs with higher integration level and lower cost. Significant efforts on the study of both devices and circuits also substantiate the wireless communication systems operating toward higher frequencies. Using the K-band (18 – 26.5 GHz) for short-range and high data-rate wireless communication and anti-collision radars is recently of great interest to both industry and academia [1]–[6]. Similar with other portable wireless applications, low-power design is a critical issue [6]. In this letter, we present an ultra-low-power 24 GHz low-noise amplifier (LNA) in 0.13  $\mu$ m CMOS technology. A peak gain of 9.2 dB and a minimum noise figure of 3.7 dB are achieved with a DC power consumption of 2.78 mW only.

## II. CIRCUIT TOPOLOGY AND ANALYSIS

Design of RF LNAs consists of two major parts, namely selection of transistor geometry and bias point, and also determination of circuit topology including the matching networks. The characteristics of transistors play a critical role, since the core circuit is composed of only a few transistors in most cases. In addition, a simple circuit topology is often preferred to prevent the unpredicted parasitic effects from the complicated layout.

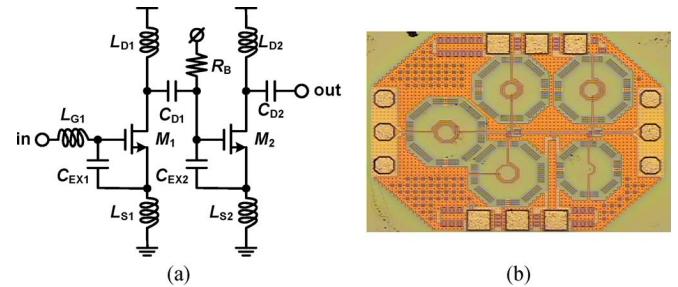

Fig. 1 shows the circuit schematic and the chip micrograph of the proposed LNA. The grounded coplanar waveguide (GCPW) is adopted for interconnects to alleviate the signal

Manuscript received August 11, 2010; accepted September 27, 2010. Date of publication November 01, 2010; date of current version December 03, 2010. This work was supported by the National Science Council under Contract NSC 97-2221-E-007-107-MY3 and by the Taiwan Semiconductor Manufacturing Company (TSMC) through National Chip Implementation Center (CIC).

The authors are with the Department of Electrical Engineering and Institute of Electronics Engineering, National Tsing Hua University, Hsinchu 300, Taiwan (e-mail: shhsu@ee.nthu.edu.tw).

Color versions of one or more of the figures in this letter are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/LMWC.2010.2085038

Fig. 1. (a) Circuit schematic and (b) chip microphotograph ( $0.76 \times 0.59 \text{ mm}^2$  with core area of  $0.59 \times 0.46 \text{ mm}^2$ ) of the proposed ultra-low-power LNA.

attenuation and substrate coupling effect [7]. In this design, two common-source (CS) stages connected in cascade are employed. As shown in Fig. 1(a), there are only two transistors in the proposed LNA, and thus determination of transistor geometry and bias is of extreme importance for achieving low-noise and low-power simultaneously.

### A. Determination of Transistor Bias and Geometry

Differing from the previous study mainly using the noise figure *NF* to select the transistor size in LNA design [8], the noise measure *M* is adopted here. *M* is a calculation for cascaded noisy gain stages to determine which one should be used first for achieving the lowest noise figure [9]. Calculation of *M* includes the information of both *NF* and gain, the two major concerns in LNA design. Instead of obtaining *M* by *NF* and power gain ( $S_{21}$ ) under  $50 \Omega$  terminations, we propose of using the minimum noise figure  $NF_{\text{MIN}}$  and maximum stable gain  $G_{\text{MAX}}$  to calculate noise measure (denoted as  $M_{\text{MIN}}$ )

$$M_{\text{MIN}} = \frac{10^{NF_{\text{MIN}}[\text{dB}]/10} - 1}{1 - 10^{-G_{\text{MAX}}[\text{dB}]/10}}. \quad (1)$$

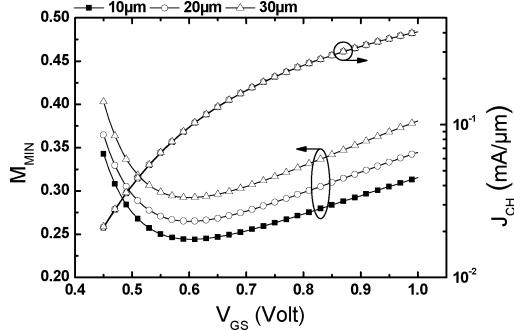

Compared with using *NF* and  $S_{21}$ ,  $NF_{\text{MIN}}$  and  $G_{\text{MAX}}$  indicate the best possible performance can be achieved after matching, and hence  $M_{\text{MIN}}$  provides a pertinent guideline on the transistor bias and geometry determination. Fig. 2 plots  $M_{\text{MIN}}$  and current density  $J_{\text{CH}}$  as a function of the gate bias ( $V_{\text{DD}} = 1 \text{ V}$ ) for 0.13  $\mu$ m NMOS based on the foundry provided transistor model (BSIM3v3) with three typical channel widths of 10, 20, and 30  $\mu$ m. The excellent scalability of MOS transistors results in three almost identical curves of  $J_{\text{CH}}$ . In addition, the optimal  $M_{\text{MIN}}$  always occurs, independent of the channel width, in a small range of  $J_{\text{CH}}$ . The corresponding  $V_{\text{GS}}$  is at around 0.55–0.65 V. By also considering power consumption and gain, the finally selected gate bias is 0.6 V, mapping to  $J_{\text{CH}}$  of about 0.1 mA/ $\mu$ m. Compared with  $M_{\text{MIN}}$ , the noise measure *M* is not helpful in this case since matching of the

Fig. 2.  $M_{MIN}$  and  $J_{CH}$  versus gate bias,  $V_{GS}$ , for transistors of  $W/L = 2 \mu\text{m}/0.13 \mu\text{m}$  with 5, 10, 15 fingers, respectively, at 24 GHz.

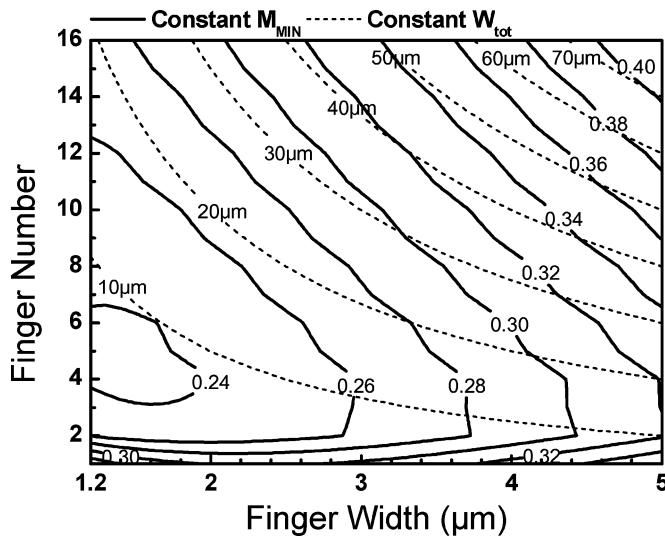

Fig. 3. Contour plot of  $M_{MIN}$  and the total finger width for  $0.13 \mu\text{m}$  NMOS under  $V_{GS} = 0.6$  V and  $V_{DD} = 1$  V at 24 GHz.

transistor is not considered. Without matching, the transistor has an intrinsic gain  $S_{21}$  less than 0 dB at 24 GHz and negative  $M$ .

Fig. 3 shows the contour plot of  $M_{MIN}$  and total width  $W_{tot}$  under a fixed  $V_{GS}$  of 0.6 V ( $V_{DD} = 1$  V) using the finger width and number as the variables for the x-axis and y-axis, respectively. Considering these two parameters separately allows minimizing the undesired parasitics of the gate resistance and capacitance. Compared with the previous study [8] using  $W_{tot}$  (x-axis) and the drain current  $I_D$  (y-axis) as the variables, the proposed approach provides more information about parasitics for high frequency design optimization.

In general, as shown in Fig. 3,  $M_{MIN}$  reduces with  $W_{tot}$  and the trend is consistent with that observed in Fig. 2. The contour plot indicates that the optimal  $M_{MIN}$  ( $< 0.24$ ) occurs when the finger number is about 3 to 7 and with the finger width around 1.2 to 2  $\mu\text{m}$ . Note the width of 1.2  $\mu\text{m}$  is the smallest allowed finger width, limited by the technology. The transistor size finally employed in our design is  $1.2 \mu\text{m} \times 0.13 \mu\text{m}$  with 10 fingers, which is the optimal geometry that still remains unconditionally stable (verified by the stability factor  $K$ ) and a good power gain of the circuit after matching. If a transistor smaller than this size is used, the input/output impedances become very close to edge of the Smith chart and high Q matching

networks are required, which makes the circuit unstable. Since the power consumption is proportional to  $W_{tot}$ , this is also the smallest size and therefore, the lowest power consumption can be achieved under the criteria of unconditional stability.

### B. Circuit Topology and Matching Network

As shown in Fig. 1, the input matching network includes inductors  $L_{G1}$  and  $L_{S1}$ , and capacitor  $C_{EX1}$ . The extra gate-source capacitance is critical for achieving power-constrained simultaneous noise and input matching (PCSNIM) with both  $Z_{in}$  and  $Z_{opt}$  at  $50 \Omega$ , where  $Z_{opt}$  is the source impedance for optimal noise matching. The  $Z_{in}$  and  $Z_{opt}$  of a CS stage matching by inductor degeneration can be simplified as (modified from [10])

$$Z_{in} = \frac{g_m L_s}{C_{gs}} + j \left[ \omega L_s - \frac{1}{\omega C_{gs}} \right] \quad (2)$$

$$Z_{opt} = \frac{\alpha'}{\omega C_{gs}} - j \left[ \omega L_s - \frac{1 - \beta'}{\omega C_{gs}} \right] \quad (3)$$

where  $\alpha'$  and  $\beta'$  are both technology dependent constants. Note  $\beta'$  becomes much smaller than one in advanced technology resulting in a similar imaginary part of  $Z_{in}$  and  $Z_{opt}$ . The real part of  $Z_{opt}$  could be optimized approaching  $50 \Omega$  through  $C_{gs}$ . Estimated by the equations, a large  $C_{gs}$  of 42.8 fF ( $\sim 50$  fF from simulation), i.e., a transistor with a larger channel width is required (the intrinsic  $C_{gs}$  of the  $1.2 \mu\text{m} \times 0.13 \mu\text{m} \times 10$  device is only  $\sim 14$  fF) making it difficult for low-power design. An external capacitance is used to increase the effective gate-source capacitance while maintaining a small transistor size. Since the transistor bias and geometry are selected, the  $g_m$  of the transistor is fixed. A gate inductor  $L_g$ , as shown in Fig. 1, is essential to eliminate the imaginary part of both  $Z_{opt}$  and  $Z_{in}$  for achieving the PCSNIM condition.

The drain inductor  $L_{D1}$  functions as the load for the first stage and also serves as the inter-stage matching network together with  $L_{S2}$ ,  $C_{D1}$ , and  $C_{EX2}$ . The inductor  $L_{D2}$  and capacitor  $C_{D2}$  implement the  $L$ -section matching to a  $50 \Omega$  load for the output stage. With the determined transistor bias and geometry for both  $M_1$  and  $M_2$ ,  $C_{EX1}$  of 20 fF is employed, and then  $L_{G1}$  of 0.8 nH and  $L_{S1}$  of 0.5 nH turn both  $Z_{in}$  and  $Z_{opt}$  into  $50 \Omega$ . The inter-stage matching network consists of 0.6 nH  $L_{D1}$ , 150 fF  $C_{D1}$ , 20 fF  $C_{EX2}$  and 0.3 nH  $L_{S2}$ . Finally,  $L_{D2}$  of 0.7 nH and  $C_{D2}$  of 47 fF complete the output matching network. Note the smaller  $C_{EX}$  than expected is due to the Miller effect, which adds  $\sim 15$  fF to have a total equivalent  $C_{gs}$  of  $\sim 50$  fF.

### III. MEASURED RESULTS

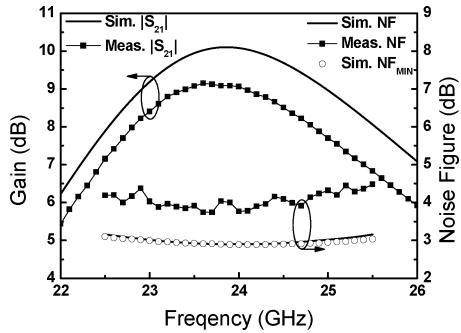

Fig. 4 shows the measured results together with the simulation. The well agreed  $NF_{MIN}$  and  $NF$  from simulation at around 24 GHz with excellent  $S_{11}$  (see Fig. 5) indicate that the PCSNIM condition is obtained. Under a supply voltage of 1 V and bias current of 2.78 mA, a peak gain of 9.2 dB and a minimum noise figure of 3.7 dB were achieved both at 23.6 GHz from measurements. Since the passive components are carefully simulated by the EM simulation tool, the discrepancy between simulated and measured results could be mainly attributed to the modeling of active devices, in which some parasitic effects may

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH PUBLISHED WORKS

| Ref.                         | This work          | [2]                | [3]   | [4]      | [5]                | [6]                |

|------------------------------|--------------------|--------------------|-------|----------|--------------------|--------------------|

| Technology (CMOS)            | 0.13 $\mu\text{m}$ | 0.18 $\mu\text{m}$ | 90 nm | 90 nm    | 0.18 $\mu\text{m}$ | 0.18 $\mu\text{m}$ |

| Peak gain frequency (GHz)    | 23.6               | 24                 | 33    | 28.5     | 24                 | 22                 |

| Power gain (dB)              | 9.2                | 13.1               | 18.6  | 20       | 12.8               | 10.1               |

| Bandwidth (GHz)              | 22.2-25.9          | 22-26.5            | 31-34 | 27.5-30  | 22.3-26.5          | 19.9-24            |

| Noise figure (dB)            | 3.7                | 3.9                | 3     | 2.9      | 3.3                | 4.3                |

| I/O return losses (dB)       | 12/16              | 15/20              | 8/18  | 12/17    | 7.5/17             | 12/-               |

| $P_{\text{LdB}}/IIP_3$ (dBm) | -13/-2.9           | -12.2/+0.54        | -16/- | -17/-7.5 | -/-                | -10/-1             |

| $P_{\text{DC}}$ (mW)         | 2.78               | 14                 | 10    | 16.25    | 8                  | 7.2                |

| Power supply (Volt)          | 1                  | 1                  | 1.2   | 1        | 1                  | 1.8                |

| FoM                          | 4.53               | 1.45               | 2.79  | 1.62     | 2.92               | 1.74               |

Fig. 4. Simulated and measured gain and noise figure.

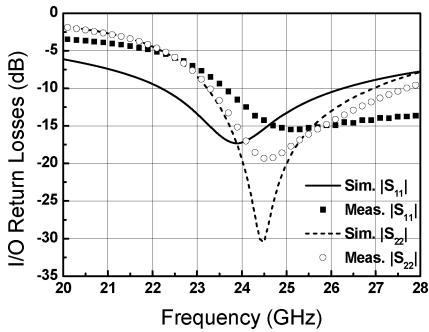

Fig. 5. Simulated and measured input/output return losses.

not be considered at high frequencies. In addition, the BSIM3v3 model does not consider the induced gate noise and use the noise model parameter  $\gamma$  of only 2/3 (should be  $> 1$  in advanced technology [10]), which result in underestimated circuit noise, as commonly seen in previous publications [2], [6]. The input and output return losses are 12 dB and 16 dB at 24 GHz respectively as shown in Fig. 5.

It should be mentioned that an external gate resistance  $r_g$  is used in the model to fit the measured noise characteristics according to the technology notes provided by the foundry. In theory, the effect of the induced gate noise can be incorporated in  $r_g$  for a better prediction of noise parameters [11]. Although the induced gate noise is not included in the model,  $r_g$  somehow corrects the model for a more accurate  $Z_{\text{opt}}$  leading to a good agreement between the simulated and measured results for PCSNIM. From the measurements, a good input matching ( $|S_{11}| < -10$  dB) is obtained in the frequency range with lowest noise figures ( $\sim 24$  GHz), which also suggests that the

PCSNIM condition is valid. Performance summary and comparison with prior arts are shown in Table I. The figure of merit (FoM) adopted is defined in [3], [5]. With a low  $NF$  and a high gain under very low power consumption, the proposed LNA achieves an excellent FoM

$$\text{FoM} = \frac{S_{21}[\text{dB}] \cdot BW[\text{GHz}]}{(NF[\text{dB}] - 1) \cdot P_{\text{DC}}[\text{mW}]} \quad (4)$$

#### IV. CONCLUSION

An ultra-low-power 24 GHz LNA was demonstrated in 0.13  $\mu\text{m}$  CMOS technology with a peak gain of 9.2 dB and a minimum  $NF$  of 3.7 dB consuming only 2.78 mW under 1 V power supply. With the proposed design approach using  $M_{\text{MIN}}$  and PCSNIM technique, the LNA presents FoM among the best compared with the published results.

#### REFERENCES

- [1] J. Jin and S. Hsu, "A 0.18- $\mu\text{m}$  CMOS balanced amplifier for 24-GHz applications," *IEEE J. Solid-State Circuits*, vol. 43, no. 2, pp. 440-445, Feb. 2008.

- [2] S. Shin, M. Tsai, R. Liu, K. Lin, and H. Wang, "A 24-GHz 3.9-dB NF low-noise amplifier using 0.18  $\mu\text{m}$  CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 7, pp. 448-450, Jul. 2005.

- [3] M. A. T. Sanduleanu, G. Zhang, and J. R. Long, "31-34 GHz low noise amplifier with on-chip microstrip lines and inter-stage matching in 90-nm baseline CMOS," in *Proc. IEEE RFIC Symp.*, 2006, pp. 143-145.

- [4] E. Adabi, B. Heydari, M. Bohsali, and A. M. Niknejad, "30 GHz CMOS low noise amplifier," in *Proc. IEEE RFIC Symp.*, 2007, pp. 625-628.

- [5] A. Sayag *et al.*, "A 25 GHz 3.3 dB NF low noise amplifier based upon slow wave transmission lines and the 0.18  $\mu\text{m}$  CMOS technology," in *Proc. IEEE RFIC Symp.*, 2008, pp. 373-376.

- [6] Y. Wei, S. Hsu, and J. Jin, "A low-power low-noise amplifier for K-band applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 2, pp. 116-118, Feb. 2009.

- [7] Y. Lin, S. Hsu, J. Jin, and C. Chan, "A 3.1-10.6 GHz ultra-wideband CMOS low noise amplifier with current-reused technique," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 3, pp. 232-234, Mar. 2007.

- [8] A. Bevilacqua and A. M. Niknejad, "An ultrawideband CMOS low-noise amplifier for 3.1-10.6-GHz wireless receivers," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2259-2268, Dec. 2004.

- [9] G. Gonzalez, *Microwave Transistor Amplifier Analysis and Design*, 2 ed., Englewood Cliffs, NJ: Prentice Hall, 1996.

- [10] T. Nguyen *et al.*, "CMOS low-noise amplifier design optimization techniques," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 5, pp. 1433-1442, May 2004.

- [11] D. Shaeffer and T. Lee, "A 1.5-V, 1.5-GHz CMOS low noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 745-759, May 1997.