7. S.W. Su, Concurrent dual-band six-loop-antenna system with wide 3-dB beamwidth radiation for MIMO access points, *Microwave Opt Technol Lett* 52 (2010), 1253–1258.

8. S.W. Su, High-gain, short-circuited six-monopole-antenna system for concurrent, dual-band WLAN access points, *Microwave Opt Technol Lett* 52 (2010), 2728–2732.

9. S.W. Su and T.C. Hong, Printed, multi-loop-antenna system integrated into a concurrent, dual-WLAN-band access point, *Microwave Opt Technol Lett* 53 (2011), 317–322.

10. H. Morishita, Y. Kim, and K. Fujimoto, Design concept of antennas for small mobile terminals and the future perspective, *IEEE Antennas Propag Mag* 44 (2002), 30–34.

11. IEEE 802.11j-2004, Wikipedia, the free encyclopedia, [http://en.wikipedia.org/wiki/IEEE\\_802.11j-2004](http://en.wikipedia.org/wiki/IEEE_802.11j-2004).

12. CTIA authorized test laboratory, CTIA, the wireless association, available at [http://www.ctia.org/business\\_resources/certification/test\\_labs/](http://www.ctia.org/business_resources/certification/test_labs/).

13. Free-space path loss, Wikipedia, the free encyclopedia, [http://en.wikipedia.org/wiki/Free-space\\_path\\_loss](http://en.wikipedia.org/wiki/Free-space_path_loss).

© 2012 Wiley Periodicals, Inc.

## A V-BAND LOW-NOISE AMPLIFIER CO-DESIGNED WITH ESD NETWORK IN 65-nm RF CMOS

Ming-Hsien Tsai and Shawn S. H. Hsu

Department of Electrical Engineering and Institute of Electronics Engineering, National Tsing Hua University, 101, Sec. 2, Kuang-Fu Road, Hsinchu, Taiwan 300, Republic of China; Corresponding author: shhsu@ee.nthu.edu.tw

Received 18 May 2011

**ABSTRACT:** A V-band low-noise amplifier (LNA) with electrostatic discharge (ESD) protection using RF junction varactors is demonstrated in a 65-nm CMOS technology. The gate-source junction varactor is used to achieve a power-constrained simultaneous noise and input matching, and also as an auxiliary ESD protection for the NS and ND modes. The measured results shows an over 2.0-kV ESD protection in the PD and PS modes, whereas the ESD level is enhanced up to 4.0 kV in the NS and ND modes. Under a power consumption of only 14.1 mW, the LNA demonstrates a noise figure (NF) of 5.2 dB and a peak power gain of 10.9 dB at 51 GHz, only a 0.8-dB degradation for both NF and power gain compared with the reference design (LNA without ESD protection). © 2012 Wiley Periodicals, Inc. *Microwave Opt Technol Lett* 54:820–822, 2012; View this article online at [wileyonlinelibrary.com](http://wileyonlinelibrary.com). DOI 10.1002/mop.26623

**Key words:** CMOS; electrostatic discharge; low-noise amplifier; V-band

### 1. INTRODUCTION

The CMOS technology with rapid feature size scaling demonstrates integrated circuits capable of high speed and low power applications. Studies have been reported recently by using advanced CMOS technology to realize receiver circuits for high data rate wireless communications [1–3]. As the first stage of an RF receiver, the low-noise amplifier (LNA) is exposed directly under the risk of electrostatic discharge (ESD), and hence it is essential to provide ESD protection at the RF input pin of the LNA. Design of ESD network becomes a more challenging task in advanced CMOS technology with the reduced gate oxide thickness and lowered breakdown voltage. The increased operation frequency also makes the noise figure (NF) and gain of the LNA more sensitive to the parasitics introduced by the ESD protection devices [3–6].

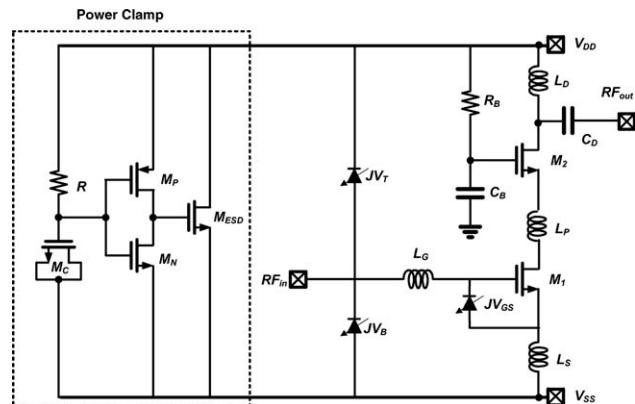

**Figure 1** Circuit schematic of the proposed V-band LNA with ESD protection network

In this study, an ESD-protected LNA is proposed using RF junction varactors for noise optimization and ESD robustness enhancement simultaneously. By codesigning the ESD/input matching network, a V-band ESD-protected LNA with a one-stage cascode configuration is demonstrated in 65-nm CMOS. Under a power consumption of only 14.1 mW, the proposed ESD-protected LNA achieves an over 2-kV Human-body-mode ESD protection (over 4-kV for NS and ND modes), a peak power gain of 10.9 dB, and a NF of 5.2 dB at 51 GHz. The NF and power gain are both degraded by only 0.8 dB compared with the reference design.

### 2. LNA DESIGN

Figure 1 shows the circuit schematic of the core LNA together with the ESD network. The LNA is basically a cascode configuration with inductive source degeneration, which has the advantage of good isolation and the capability of simultaneous noise and impedance matching. The input matching network includes

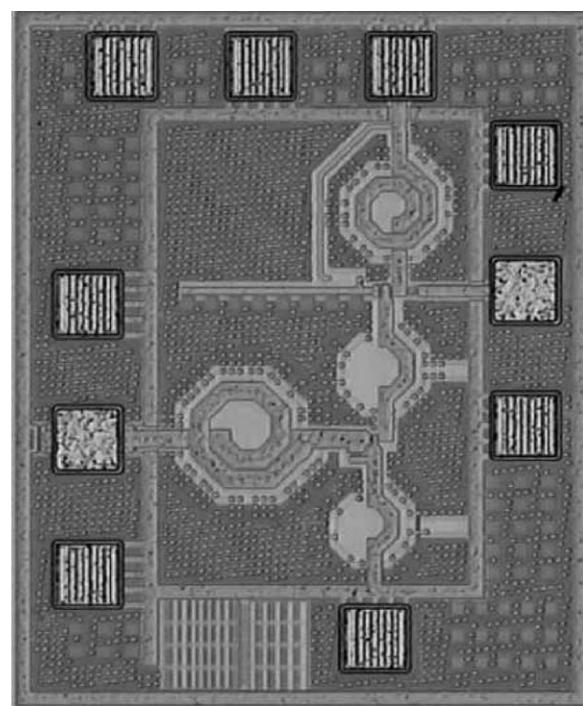

**Figure 2** Chip microphotograph (Chip area: 0.51 × 0.41 mm<sup>2</sup>)

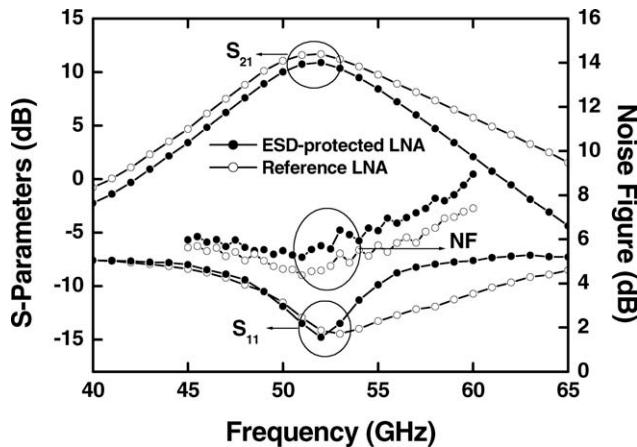

**Figure 3** Measured S-parameters and NFs of the LNAs with/without ESD protection

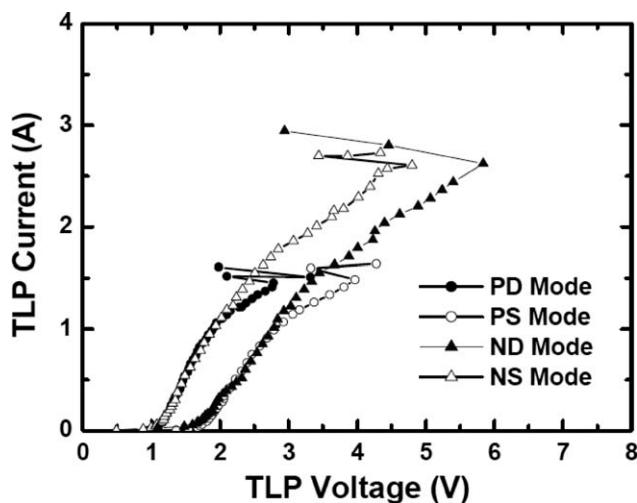

**Figure 4** Measured TLP I-V curves of the proposed ESD-protected LNA

two junction varactors JVT and JVB (also used as ESD devices), gate inductor LG, source inductor LS, and the gate-source junction varactor JVGS (also used for power-constrained simultaneous noise and input matching (PCSNIM) and ESD enhancement simultaneously). All the elements for input matching are co-optimized in the beginning of LNA design, and hence the performance degradation due to the extra ESD network can be minimized. The inductor LP inserted between the common-

source and common-gate stage of the cascode configuration is used for gain peaking, and also resonating with the parasitic capacitances to improve output matching [7]. The drain inductor LD and capacitor CD are used for the output-matching network in the 50- $\Omega$  measurement environment. The dual-diode topology (JVT and JVB) is used for the ESD devices at the RF input to provide the direct ESD current paths for the PD and NS modes. The power clamp consists of RC (resistor R and MOS capacitor MC) and inverter (MP and MN) to trigger the large NMOS (MESD), which provides a low-impedance path from VDD to ground and completes the ESD paths for PS and ND modes. An extra gate-source MIM capacitor is widely used for the input stage of LNA design to achieve PCSNIM [8]. In this study, instead of using the conventional MIM capacitor, the junction varactor JVGS is adopted, serving as the extra gate-source capacitance for low power design. Simultaneously, JVGS will turn on under forward bias during ESD zapping, providing an additional ESD current path to enhance the ESD level for both the NS and ND modes.

### 3. RESULTS AND DISCUSSION

Figure 2 shows the chip micrograph of the proposed ESD-protected LNA fabricated in a 65-nm CMOS technology, in which the chip area is  $0.41 \times 0.51 \text{ mm}^2$  including the probing pads for on-wafer testing both RF and ESD characteristics. The reference design (LNA without ESD protection) with the same chip size was also realized. Figure 3 shows the measured  $S_{11}$ ,  $S_{21}$ , and NFs of the LNA with and without the ESD protection, respectively. The ESD-protected LNA presents a peak power gain of 10.9 dB, an input return loss of greater than 10 dB, and a NF of 5.2 dB at 51 GHz. Compared with the reference design, both the peak gain and NF only degrade by 0.8 dB. The measured third-order-intercept point IIP3 of both LNAs are about  $-10 \text{ dBm}$  at 51 GHz, which indicates that using the RF junction varactors as the ESD devices does not have significant impacts on LNA linearity. The ESD testing was performed using the Barth 4002 transmission line pulse (TLP) test system. Figure 4 shows the TLP I-V characteristics of four different testing modes (PD, PS, ND, and NS) for the ESD-protected LNA [6]. A second breakdown current  $I_{t2}$  up to  $\sim 1.4 \text{ A}$  can be achieved, corresponding to an ESD level of 2.0 kV in the PD and PS modes. In both ND and NS modes,  $I_{t2}$  is up to  $\sim 2.6 \text{ A}$ , corresponding to an ESD level of 4.0 kV. By taking the ESD level and chip size into consideration, a figure-of-merit (FOM, modified from Ref. 4), consisting of gain, input third-order intercept point (IIP3), operating frequency (fC), dc power consumption, NF, chip area, and ESD level, is used to quantify both ESD and RF performance for RF LNAs. Table 1 summarizes the circuit performance and compares the proposed ESD-protected LNA with

**TABLE 1** Performance Comparison of the Proposed ESD-Protected LNAs with Prior Art

| Ref.                    | [3]  | [4]     | [5]   | [6]    | This Work |

|-------------------------|------|---------|-------|--------|-----------|

| Tech. (nm)              | 130  | 90      | 90    | 65     | 65        |

| Freq. (GHz)             | 60   | 5.5     | 2.4   | 5.8    | 51        |

| NF (dB)                 | 7.2  | 8.6     | 2.7   | 1.85   | 2.57      |

| Power (mW)              | 65   | 65      | 9.72  | 12.9   | 7.8       |

| $S_{21}$ (dB)           | 20.2 | 20.4    | 13.3  | 22.1   | 18.1      |

| $S_{11}$ (dB)           | -15  | -15     | -10.3 | -12.66 | -10.99    |

| IIP3 (dBm)              | -12  | -12     | -3    | -10.83 | -11.01    |

| HBM (kV)                | -    | 6.5/1.5 | -     | 4      | 6.5       |

| Area (mm <sup>2</sup> ) | 0.48 | 0.715   | 0.72  | 0.94   | 0.55      |

| FOM                     | **   | 0.9/0.2 | **    | 2.9    | 0.5       |

prior arts. The proposed LNA shows an FOM among the best compared with the published results in the table.

$$FOM = \frac{\text{Gain[abs]} \times \text{IIP3[abs]} \times f_C[\text{GHz}] \times \text{ESD[kV]}}{(\text{NF} - 1)[\text{abs}] \times P_{\text{DC}}[\text{mW}] \times \text{Area}[\text{mm}^2]}$$

#### 4. CONCLUSIONS

A V-band LNA with ESD protection network was realized in 65-nm CMOS technology using the proposed RF junction varactors as the ESD devices. Under a power consumption of only 14.1 mW, the LNA demonstrated a NF of 5.2 dB with an associated power gain of 10.9 dB, only a 0.8-dB degradation of both power gain and NF compared with the reference LNA. The proposed gate-source junction varactor design technique successfully enhanced the ESD protection level from 2.0 to 4 kV for the ND and NS modes.

#### REFERENCES

1. E. Ragonese, A. Scuderi, and G. Palmisano, A transformer-loaded variable-gain LNA for 24-GHz vehicular short-range radar, *Microwave Opt Technol Lett* 50 (2008), 2013–2016.

2. Y. Cao, V. Issakov, and M. Tiebout, A 2kV ESD-protected 18 GHz LNA with 4dB NF in 0.13 μm CMOS, *Technical Digest of ISSCC*, San Fransisco, CA (2008), 194–195.

3. B. Huang, C. Wang, C. Chen, M. Lei, P. Huang, K. Lin, and H. Wang, Design and analysis for a 60-GHz low-noise amplifier with RF ESD protection, *IEEE Trans Microwave Theory Tech* 57 (2009), 298–305.

4. D. Linten, S. Thijs, M. Natarajan, P. Wambacq, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S. Donnay, and S. Decoutere, A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS, *IEEE J Solid-State Circuits* 40 (2005), 1434–1442.

5. C. Chang, J. Hou, J. Su, C. Chen, T. Liou, S. Wong, and Y. Wang, A high gain and low supply voltage LNA for the direct conversion application with 4-kV HBM ESD protection in 90-nm RF CMOS, *IEEE Microwave Wirel Compon Lett* 16 (2006), 612–614.

6. M. Tsai, S. Hsu, F. Hsueh, and C. Jou, A multi-ESD-path low-noise amplifier with a 4.3-A TLP current level in 65-nm CMOS, *IEEE Trans Microwave Theory Tech* 58 (2010), 4004–4011.

7. H. Zhang, X. Fan, and E.S. Sinencio, A low-power, linearized, ultra-wideband LNA design technique, *IEEE J Solid-State Circuits* 44 (2009), 320–330.

8. T. Nguyen, C. Kim, G. Ihm, M. Yang, and S. Lee, CMOS low-noise amplifier design optimization techniques, *IEEE Trans Microwave Theory Tech* 52 (2004), 1433–1442.

© 2012 Wiley Periodicals, Inc.

## FIBER BRAGG GRATING CURRENT SENSOR BASED ON BIREFRINGENCE EFFECT

**Yong Zhao and Ting-Ting Song**

Northeastern University, College of Information Science and Engineering, Shenyang 110819, China; Corresponding author: zhaoyong@ise.neu.edu.cn

Received 24 May 2011

**ABSTRACT:** A novel DC current sensor configuration by combining the sensing theory of fiber Bragg grating (FBG) with the birefringence effect is proposed. Electromagnet force will occur when the measured current is applied due to the sensor configuration of a magnetic coil and

a permanent magnet. A sensing FBG and a supporting fiber with the same diameter and material are inserted between two glass sheets. The electromagnet force will act on the glass sheets, resulting in a radial load on the sensing FBG. This transverse load will lead to the birefringence effect because of the different strain or refractive index variation of the two orthogonal axes of the sensing fiber. Thus, two orthogonal polarization modes will be reflected by the sensing FBG with different wavelengths. The theoretical model between Bragg wavelength shifts versus the applied current is derived. Preliminary experiments and simulation results show that current measurement sensitivity can reach 2 nm/A, and measurement resolution is about 0.5 mA. Cross-sensitivity of temperature can be compensated by the differential method. © 2012 Wiley Periodicals, Inc. *Microwave Opt Technol Lett* 54:822–826, 2012; View this article online at [wileyonlinelibrary.com](http://wileyonlinelibrary.com). DOI 10.1002/mop.26609

**Key words:** fiber Bragg grating sensor; current sensor; birefringence effect; transverse load; wavelength shift

#### 1. INTRODUCTION

Several physical principles and effects can be used as the basis of the fiber optic current sensors, such as the electromagnetic induction effect, the Faraday rotation effect, the magnetostrictive effect, the heat effect, the converse piezoelectric effect, the electromagnetic force effect, and so on [1–4]. A traditional Rogowski coil is often used to sample the transmission-line current in those fiber optic current sensors based on the electromagnetic induction effect. So, it is not an all-optical fiber current sensor.

The current sensors based on the principles of magnetostrictive effect, the heat effect, the converse piezoelectric effect, and the electromagnetic force effect could be classified as one sort because the measured current will lead to a force or a displacement, acting on the sensing fibers or fiber Bragg gratings (FBGs). For example, the expansion of the magnetostrictive material under an electromagnetic condition will lead to a length variation of the sensing fiber, which is fixed on the surface of the magnetostrictive material. The length variation will cause the optical phase variation of the fiber optic interferometer. For those FBG current sensors using magnetostrictive effect, the FBG is fixed on the surface of the magnetostrictive material, and the expansion will cause the reflected wavelength shift of the Bragg grating [2]. In these kinds of sensors, the fibers are all glue-bonded on the magnetostrictive material; load effect will occur at the bonding point, leading to the hysteresis effect with increase in the measured current. There are two kinds of electromagnetic force-based fiber current sensors. One is to change the cavity length of the F-P interferometer due to the electromagnetic force-generated displacement [3], and the other is to change reflected wavelength of the FBG sensor due to the electromagnetic force-generated deformation [4].

In this article, a FBG current sensor based on the birefringence effect is proposed. The electromagnetic force generated by the measured current transversely acts on the sensing FBG in the radial direction, resulting in the birefringence effect, which leads to the reflected spectrum separation of the two polarization states. By measuring the wavelength difference between the two polarization states, the relationship between the wavelength difference and the measured current will be established.

#### 2. SENSING STRUCTURE AND MEASUREMENT PRINCIPLE

##### 2.1. Sensing Structure

The schematic diagram of the proposed FBG current sensor system is shown as in Figure 1. In the sensor probe, a sensing FBG