# Interfacial trap characteristics in depletion mode GaAs MOSFETs

T.C. Lee<sup>a</sup>, C.Y. Chan<sup>b</sup>, P.J. Tsai<sup>c</sup>, Shawn S.H. Hsu<sup>b</sup>, J. Kwo<sup>d</sup>, M. Hong<sup>c,\*</sup>

<sup>a</sup>*Electronics and Optoelectronics Research Laboratory, Industrial Technology Research Institute, Hsinchu, Taiwan*

<sup>b</sup>*Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan*

<sup>c</sup>*Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu, Taiwan*

<sup>d</sup>*Department of Physics, National Tsing Hua University, Hsinchu, Taiwan*

Available online 30 January 2007

## Abstract

The trap-related characteristics in depletion mode GaAs metal-oxide-semiconductor field-effect-transistors (MOSFETs) were studied using two different electrical characterization techniques of current collapse and low-frequency noise measurements. With a high-quality MBE-grown gate oxide layer  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3) \sim 30 \text{ nm}$  thick in situ on GaAs, an extremely small drain current collapse factor  $\Delta I_{\max}$  of less than 5% was observed even with a high drain bias of 16 V. In addition, no kink effect was observed in the low-frequency AC  $I$ - $V$  characteristics. Moreover, a normalized drain noise current spectral density in the range of  $10^{-11}$ – $10^{-9} \text{ Hz}^{-1}$  (at 10 Hz) was obtained, which is comparable to modern 0.13- $\mu\text{m}$  Si complementary MOS (CMOS) technology under similar biasing conditions. The results indicate low interfacial trap densities for the studied GaAs MOSFETs.

© 2007 Elsevier B.V. All rights reserved.

PACS: 71.55.eq; 73.20.at; 73.40.qv; 73.61.ey

Keywords: A1. Characterization; A3. MBE; B2. Dielectric; B2. GaAs; B3. Field effect transistor; B3. MESFET

## 1. Introduction

The GaAs metal-oxide-semiconductor field-effect-transistors (MOSFETs), due to the superior electron mobility of GaAs and the availability of semi-insulating substrates, have great advantages over their Si-based counterparts for high-speed, low-power logic integrated circuits. Compared to the conventional GaAs-based FETs, such as metal-semiconductor FETs (MESFETs) and high electron mobility transistors (HEMTs), which exhibit small forward gate voltage operation limited by the Schottky barrier, the GaAs MOSFETs allow a much larger logic swing for greater flexibility in circuit design.

The GaAs MOSFETs, after extensive pursuing over the past few decades, have been realized with a solution in the molecular beam epitaxy (MBE) grown  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$  in situ deposited on GaAs [1–7]. A low interfacial density of state less than  $10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ , has been attained. The employment of  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$  as the gate dielectric has led

to the demonstration of the first inversion-channel GaAs MOSFET [3–5]. The DC and RF characteristics of depletion-mode (D-mode) GaAs MOSFETs have demonstrated a drain current density up to 450 mA/mm and, an  $f_T$  and  $f_{\max}$  of 17 and 60 GHz, respectively [6,7].

However, the trap-related device characteristics with  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$  as a gate dielectric, have not been reported and analyzed in detail. In this study, the current collapse and the flicker noise measurements are employed to study the trap characteristics of the interface between  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$  and GaAs. A low interfacial trap density of the devices has been identified, which also provides valuable information on possible noise origins and directions to further improve the material quality and device performance.

## 2. Experimental procedure

The sample growth was performed in a multi-chamber MBE system, which includes a solid source GaAs-based MBE chamber, an arsenic-free oxide UHV chamber, and in situ transfer modules [1]. All chambers are connected via

\*Corresponding author. Tel.: +886 3 5742283; fax: +886 3 5722366.

E-mail address: [mhong@mx.nthu.edu.tw](mailto:mhong@mx.nthu.edu.tw) (M. Hong).

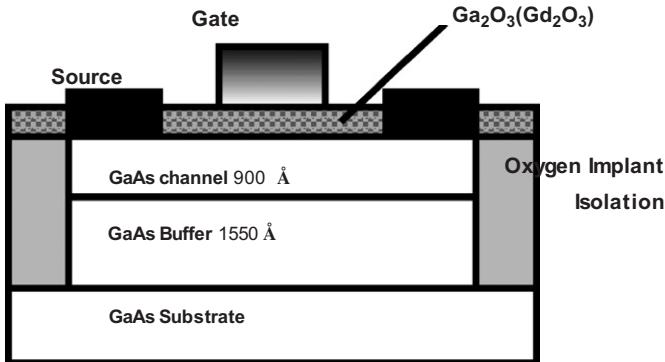

Fig. 1. The cross section of fabricated depletion-mode n-channel GaAs MOSFETs. The oxide thickness is 300 Å.

UHV transfer modules where the background pressure is maintained at less than  $10^{-10}$  Torr. Device structures, which consisted of an undoped GaAs buffer and a 900 Å GaAs channel layer with a Si doping concentration of  $4 \times 10^{17} \text{ cm}^{-3}$ , were epitaxially grown on semi-insulating GaAs (100) substrates. After the epi growth, the sample was in situ moved to the As-free oxide growth chamber. The gate dielectric of  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$  30 nm thick was deposited by electron-beam evaporation from a single crystal  $\text{Ga}_5\text{Gd}_3\text{O}_{12}$  garnet. The fabricated depletion-mode (D-mode) n-channel GaAs MOSFET was shown in Fig. 1. Device isolation was achieved by oxygen implantation (190 and 100 keV,  $1 \times 10^{14} \text{ cm}^{-2}$ ), followed by an activation annealing at 480 °C for 5 min in  $\text{N}_2$  gas ambient. Prior to metal deposition, the oxide was removed using an HCl-based solution. Then, the ohmic metal  $\text{AuGe}/\text{Ni}/\text{Au}$  with thickness 500 Å/200 Å/1500 Å was deposited, followed by a 400 °C, 5 min alloying process in a  $\text{N}_2$  ambient. The gate metal,  $\text{Ti}/\text{Pt}/\text{Au}$  (300 Å/100 Å/1200 Å), was deposited using e-beam evaporation. Finally, a post annealing at 375 °C for 3 h in forming gas ambient was used to further reduce interfacial trapped charges which were induced during the fabrication processes.

### 3. Results and discussion

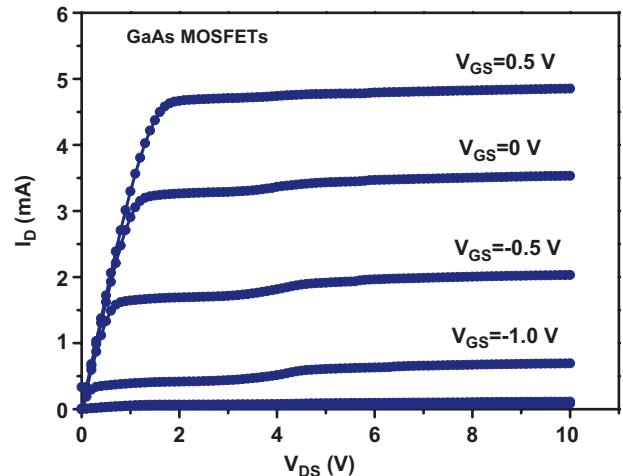

Fig. 2 presents the DC  $I-V$  curves for a device with a gate width ( $W$ ), and a gate length ( $L$ ) of 100 and 1.5  $\mu\text{m}$ , respectively. The well-defined pinch-off characteristics at  $V_{\text{GS}} = -1.5 \text{ V}$  were demonstrated. The drain current kink was observed in the saturation region of the  $I-V$  characteristics, at around  $V_{\text{DS}} = 4 \text{ V}$ , which is probably due to the interfacial charges in the open unpassivated gate region [6]. In particular, a breakdown voltage higher than 10 V was measured, which is substantially higher than typical Si-based MOSFETs and excellent for high-power applications. In addition, a large output resistance above 10 k $\Omega$  was observed in the saturation region, which is also beneficial for circuit design.

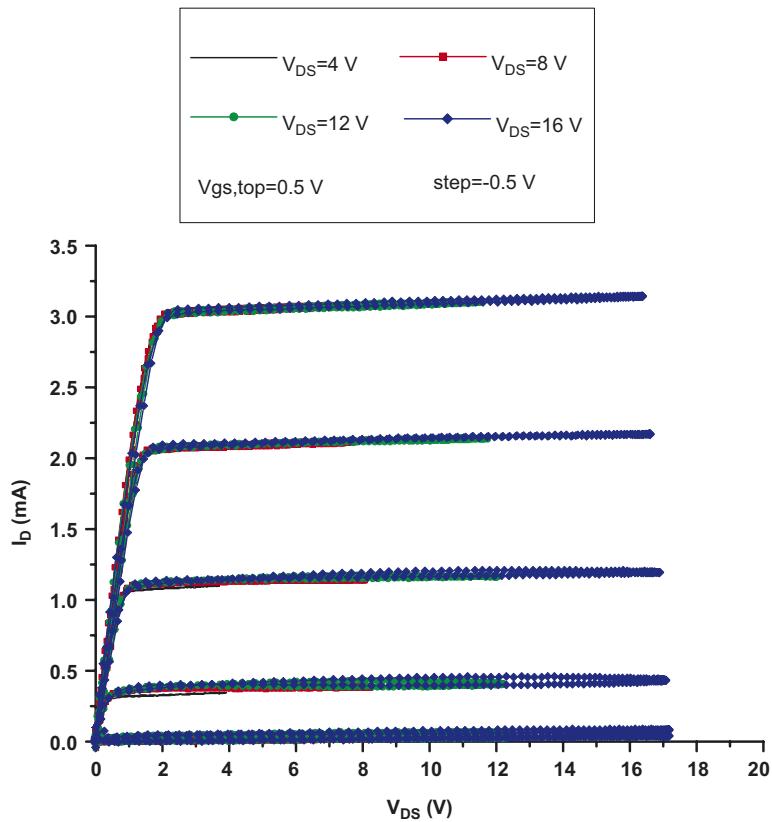

The current collapse measurement of the device was performed under the sweep of a 60 Hz rectified sine wave using a Tektronix 370 curve tracer. The response of the

Fig. 2. The DC current–voltage characteristics for depletion-mode GaAs MOSFETs with gate length 1.5  $\mu\text{m}$  and a gate width 100  $\mu\text{m}$ .

traps was probed by the slowly changed signal, and the impact of the interface traps was observed by the  $I-V$  characteristics of the devices. The measured current collapse with various  $V_{\text{d}}$  sweeps, ranging from 4 to 16 V, is shown in Fig. 3. The collapse factor,  $\Delta I_{\text{max}}$ , is defined as the ratio of the decreased maximum drain current with a  $V_{\text{d}}$  sweep of 16 V to the maximum drain current with a  $V_{\text{d}}$  sweep of 8 V. As a whole, there is no obvious drain current reduction observed, even under a very high drain bias of 16 V. The  $\Delta I_{\text{max}}$ 's are all below 5% for all gate biasing conditions.

In contrast to the DC  $I-V$  results, there is no kink observed in the current collapse measurement. These results indicated the excellent passivation of using  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$ , the novel gate dielectric in situ deposited on GaAs surface and the low interfacial state density in the oxide/GaAs interface. Compared with the previous report [6,7], the D-mode GaAs MOSFET exhibited improved  $I-V$  characteristics, with negligible drain current collapse even under very high drain biases and also no kink, due to the excellent passivation.

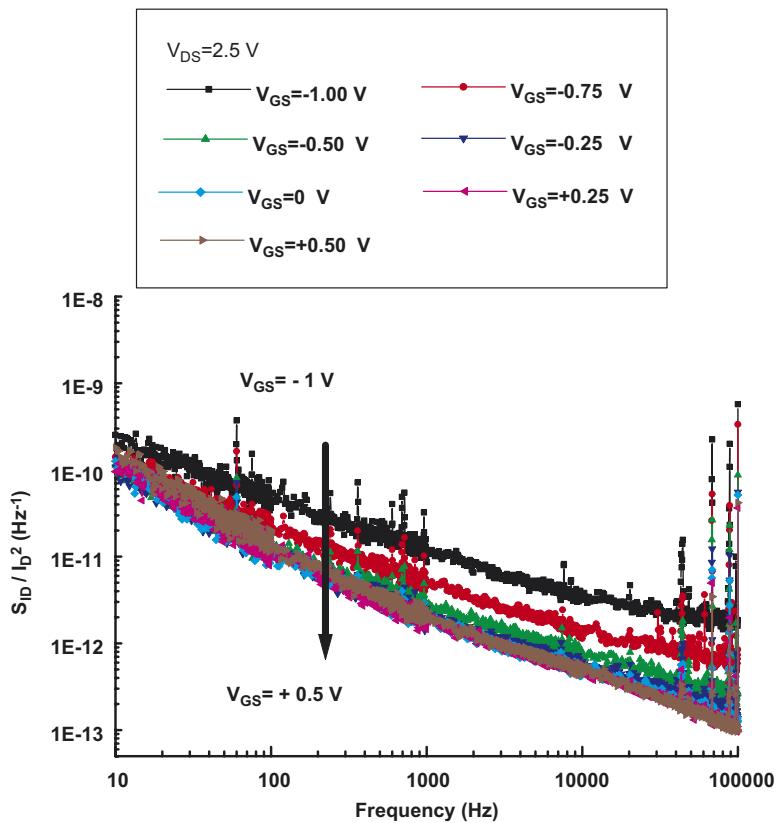

To further study the interfacial trap characteristics of the D-mode GaAs MOSFET devices, the flicker noise measurements were also performed to reveal more about the impacts of interfacial traps on these devices. Fig. 4 shows the normalized drain noise current spectral density as a function of gate bias under  $V_{\text{DS}} = 2.5 \text{ V}$ . As can be seen,  $S_{\text{ID}}/I_{\text{D}}^2$ , where  $S_{\text{ID}}$  is the drain noise current and  $I_{\text{D}}$  is drain current, reduces with increasing the gate bias, which is due to a screening effect from the channel carriers. The increase in total channel carriers as the device was biased away from pinch-off has attributed to the monotonically reduced noise density with increasing  $V_{\text{G}}$ . Compared to modern Si CMOS technology, the typical normalized noise spectral density in 0.13- $\mu\text{m}$  NMOS technology is in a range of  $10^{-11}$ – $10^{-9} \text{ Hz}^{-1}$  (at 10 Hz, under similar biasing conditions) [8], which is comparable to that in the GaAs MOSFETs reported here. Note that the comparison is

Fig. 3. The current collapse characteristics for depletion-mode GaAs MOSFETs with a gate length  $1.5\text{ }\mu\text{m}$  and a gate width  $100\text{ }\mu\text{m}$ .

Fig. 4. The normalized drain noise current spectral density for GaAs MOSFETs with  $V_{DS} = 2.5\text{ V}$  and  $V_{GS}$  from  $-1\text{ V}$  to  $0.5\text{ V}$ .

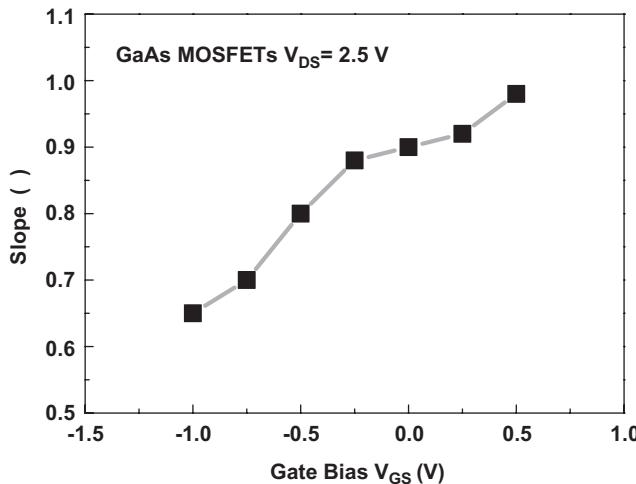

Fig. 5. The slope  $\gamma$  of the  $1/f^r$  noise spectral density under different gate biases. The drain terminal is biased at 2.5 V.

based on a normalized drain current level for both GaAs- and Si-MOSFETs, which minimizes the impact of the geometry introduced current difference on the noise level.

Fig. 5 plots the slope ( $\gamma$ ) of the  $1/f^r$  characteristics as a function of the gate bias. It was found that the extracted slope values are ranged from  $\sim 0.65$  to 1, and also increase with the gate bias. The results can be explained by the distribution of the traps in the device. Theoretically, the slope  $\gamma$  should be based on the assumption of uniformly distributed traps [9]. By employing the number fluctuation model, as the carrier tunneling distance and the trap energy are non-uniformly distributed, a gate-bias dependence of  $\gamma$  can be expected. The observed trend of  $\gamma < 1$  reveals that the trap density increases toward the  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)/\text{GaAs}$  interface. Moreover, the gate-bias dependence of  $\gamma$  suggests that trap distribution is also non-uniform as a function of energy. As the band bending increases with a higher gate bias, the amount of effective traps increase, resulting in an increased slope  $\gamma$  [9,10].

#### 4. Conclusion

The interfacial trap characteristics of the D-mode GaAs MOSFETs were investigated. There is no kink observed in

the low-frequency AC  $I-V$  characteristics. In addition, the current collapse measurement showed a negligible drain-current reduction, even with an applied drain bias up to 16 V. Investigation of the flicker noise characteristic showed a drain noise current density similar to that in modern CMOS technology. Studies on the bias dependence and the slope  $\gamma$  suggest that the main noise origin located close to the interface between  $\text{Ga}_2\text{O}_3(\text{Gd}_2\text{O}_3)$  and the channel. The various measurements all indicate a low interfacial trap density for the studied GaAs-based MOSFETs. In addition, this study identified the possible flicker noise origins and locations, which provide a direction to further improve the material quality and device performance of the GaAs MOSFETs.

#### Acknowledgments

The authors wish to thank the National Science Council, Taiwan, ROC for supporting this work.

#### References

- [1] M. Hong, J.P. Mannaerts, J.E. Bowers, J. Kwo, M. Passlack, W.-Y. Hwang, L.W. Tu, *J. Crystal Growth* 175/176 (1997) 422.

- [2] M. Hong, F. Ren, J.M. Kuo, W.S. Hobson, J. Kwo, J.P. Mannaerts, J.R. Lothian, Y.K. Chen, *J. Vac. Sci. Technol. B* 16 (3) (1998) 1398.

- [3] F. Ren, M. Hong, W.S. Hobson, J.M. Kuo, J.R. Lothian, J.P. Mannaerts, J. Kwo, Y.K. Chen, A.Y. Cho, *IEEE IEDM Conference Proceedings*, vol. 943, 1996.

- [4] F. Ren, M. Hong, W.S. Hobson, J.M. Kuo, J.R. Lothian, J.P. Mannaerts, J. Kwo, S.N.G. Chu, Y.K. Chen, A.Y. Cho, *Solid State Electron.* 41 (11) (1997) 1751.

- [5] F. Ren, J.M. Kuo, M. Hong, W.S. Hobson, J.R. Lothian, J. Lin, W.S. Tseng, J.P. Mannaerts, J. Kwo, S.N.G. Chu, Y.K. Chen, A.Y. Cho, *IEEE Electron. Dev. Lett.* 19 (8) (1998) 309.

- [6] Y.C. Wang, M. Hong, J.M. Kuo, J.P. Mannaerts, J. Kwo, H.S. Tsai, J.J. Krajewski, Y.K. Chen, A.Y. Cho, *IEEE Electron. Dev. Lett.* 20 (9) (1999) 457.

- [7] Y.C. Wang, M. Hong, J.M. Kuo, J.P. Mannaerts, J. Kwo, H.S. Tsai, J.J. Krajewski, Y.K. Chen, A.Y. Cho, *IEDM Tech. Dig.* 67 (1998).

- [8] C. Chan, J. Jin, Y. Lin, S. Hsu, Y. Juang, *ESSDERC Conference Proceedings*, September 2006.

- [9] T.G.M. Kleinpenning, L.K.J. Vandamme, *J. Appl. Phys.* 52 (1981) 1594.

- [10] E. Simoen, C. Claeys, *Solid-State Electron.* 43 (1999) 865.