## Accelerated Publication

# Drain current enhancement and negligible current collapse in GaN MOSFETs with atomic-layer-deposited $\text{HfO}_2$ as a gate dielectric

Y.C. Chang<sup>a</sup>, W.H. Chang<sup>a</sup>, Y.H. Chang<sup>a</sup>, J. Kwo<sup>b,\*</sup>, Y.S. Lin<sup>c</sup>, S.H. Hsu<sup>c</sup>, J.M. Hong<sup>d</sup>, C.C. Tsai<sup>d</sup>, M. Hong<sup>a,\*\*\*</sup>

<sup>a</sup> Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan

<sup>b</sup> Department of Physics, National Tsing Hua University, Hsinchu 30013, Taiwan

<sup>c</sup> Department of Electronics Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan

<sup>d</sup> HUGA Optotech Inc., Taichung 40768, Taiwan

## ARTICLE INFO

## Article history:

Received 1 February 2010

Accepted 17 February 2010

Available online 1 March 2010

## Keywords:

GaN

Metal-oxide-semiconductor field-effect-transistor (MOSFET)

Current collapse

$\text{HfO}_2$

Atomic layer deposition (ALD)

## ABSTRACT

Accumulation-type GaN metal-oxide-semiconductor field-effect-transistors (MOSFET's) with atomic-layer-deposited  $\text{HfO}_2$  gate dielectrics have been fabricated; a 4  $\mu\text{m}$  gate-length device with a gate dielectric of 14.8 nm in thickness (an equivalent  $\text{SiO}_2$  thickness of 3.8 nm) gave a drain current of 230 mA/mm and a broad maximum transconductance of 31 mS/mm. Owing to a low interfacial density of states ( $D_{it}$ ) at the  $\text{HfO}_2/\text{GaN}$  interface, more than two third of the drain currents come from accumulation, in contrast to those of Schottky-gate GaN devices. The device also showed negligible current collapse in a wide range of bias voltages, again due to the low  $D_{it}$ , which effectively passivate the surface states located in the gate-drain access region. Moreover, the device demonstrated a larger forward gate bias of +6 V with a much lower gate leakage current.

© 2010 Elsevier B.V. All rights reserved.

## 1. Introduction

GaN and its derivatives have been widely studied for applications in high-power devices in high electron mobility transistors (HEMT's) [1–6]. With the surface Fermi level of GaN being unpinned with  $\text{SiO}_2$  [7], and high  $\kappa$  dielectrics of  $\text{HfO}_2$  [8,9],  $\text{Al}_2\text{O}_3$  [10,11]  $\text{Gd}_2\text{O}_3$  [12,13], and  $\text{MgO}$  [14], GaN metal-oxide-semiconductor field-effect-transistors (MOSFET's) have attracted much interest lately [15–21]. The discovery of  $\text{Ga}_2\text{O}_3/\text{Gd}_2\text{O}_3$  as a gate dielectric has led to the first depletion-mode GaN MOSFET [15]. Recently, inversion-channel GaN MOSFET's were also demonstrated, with the electrical characteristics resembling that of the Si based MOSFET's [18–21].

Among the gate dielectrics,  $\text{HfO}_2$ , due to its high dielectric constant of 18–20, highly insulating electrical property and a large energy-band gap (5.4–5.8 eV), has been applied in Si CMOS and studied in III–V MOS devices [22,23]. In our previous work of GaN MOS capacitors with nanometer-thick atomic-layer-deposited (ALD)  $\text{HfO}_2$ , low electrical leakage currents and low interfacial density of states ( $D_{it}$ ) were obtained [8]; these may lead to lower gate leakage currents, a larger gate voltage sweeping range, and a sim-

pler device/circuit structure in GaN MOSFET's, compared with their counterparts of HEMT's with Schottky-gates. Moreover, the current collapse that occurs in unpassivated HEMT devices (caused by the traps existed in the regions between the gate and drain electrodes) could also be minimized/eliminated in GaN MOSFET's. The current collapse significantly reduces RF output power and degrades the device performance.

In this letter, we report a high-performance accumulation-type GaN MOSFET based on ALD- $\text{HfO}_2$  as a gate dielectric. Compared to the previously reported GaN-based MOSFET's and HEMT's, the device demonstrates excellent dc output as well as transfer characteristics, such as a high drain current ( $I_d$ ) with negligible current collapse, a high transconductance ( $G_m$ ), low gate leakage currents, and a large gate voltage sweep range.

The growth of  $\text{HfO}_2/\text{GaN}$  was described earlier, with GaN grown by metal organic chemical vapor deposition and  $\text{HfO}_2$  by ALD with tetrakis-(ethyl-methyl-amino)-hafnium (TEMAH) and  $\text{H}_2\text{O}$  as the precursors [8]. A post-deposition anneal at 600 °C was carried out under nitrogen ambience for 10 min to optimize oxide and interface quality. X-ray reflectivity measurements [24] for the annealed sample have revealed that the oxide consists of two layers with an overall thickness of 14.8 nm, bulk  $\text{HfO}_2$  (13.2 nm) and an interfacial layer  $\text{GaON}$  1.6 nm thick. The interfacial roughness was small of 0.41 nm, critical to make a high-performance device. The determination of oxide film thickness was needed for fabricating the device.

\* Corresponding author.

\*\* Corresponding author.

E-mail addresses: [raynien@phys.nthu.edu.tw](mailto:raynien@phys.nthu.edu.tw) (J. Kwo), [mhong@mx.nthu.edu.tw](mailto:mhong@mx.nthu.edu.tw) (M. Hong).

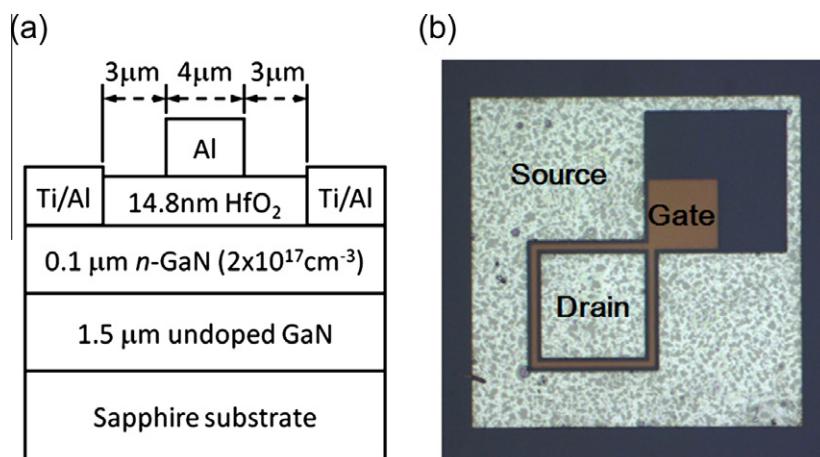

Ring-gate accumulation-type GaN MOSFET's were fabricated with a two-step process (S/D contact metal and gate metal formation). The S/D contact on the doped GaN was achieved by etching HfO<sub>2</sub> using dilute hydrofluoric acid (HF), removing the interfacial layer GaON layer using dilute hydrochloric acid (HCl), followed by e-beam evaporating metal Ti/Al (30 nm/120 nm) on GaN and rapid thermal annealing (RTA) to 600 °C and dwelling there for 30 s under nitrogen ambience. Finally, Al (120 nm) was e-beam evaporated as the gate electrodes. Both the source-to-gate and the gate-to-drain spacing are 3 μm. The schematic cross-sectional and the planar views of the fabricated ring-gate GaN MOSFET are shown in Fig. 1(a) and (b), respectively.

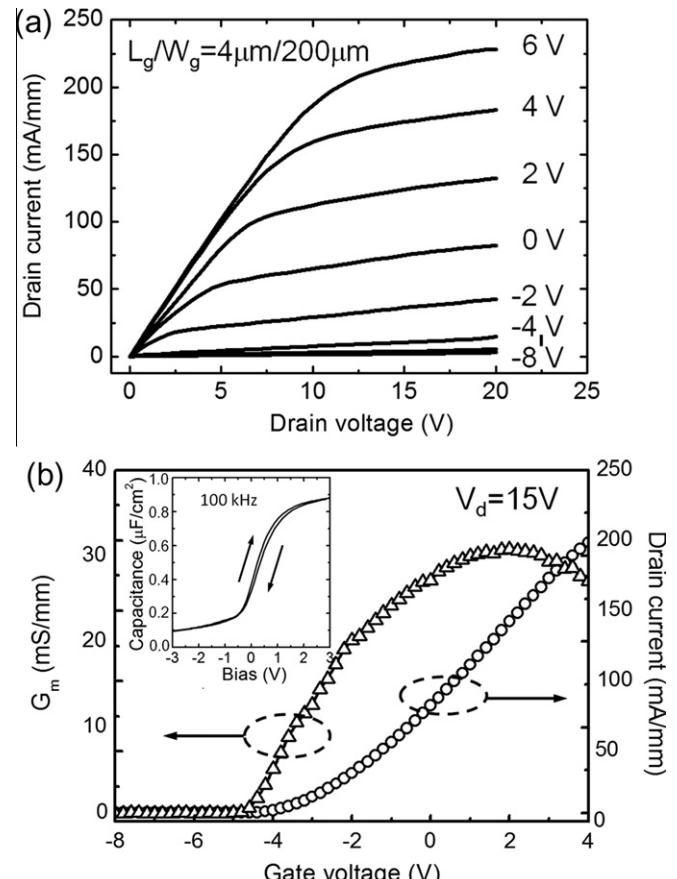

Fig. 2(a) shows the drain *I*-*V* characteristics of a 4 μm gate-length MOSFET with the gate voltage (*V*<sub>g</sub>) varying from −8 V to +6 V with a step of 2 V. The pinch-off voltage of the fabricated device is −8 V. The maximum *I*<sub>d</sub> ~ 230 mA/mm at *V*<sub>g</sub> of +6 V and a drain voltage (*V*<sub>d</sub>) of 20 V has been achieved, the highest ever reported for GaN MOSFETs, which is owing to the effective passivation of HfO<sub>2</sub>/GaN interface with a low *D*<sub>it</sub> and the high dielectric constant of HfO<sub>2</sub>. These remarkable interfacial material/electrical properties have led to a more efficient gate modulation and an accumulation of more carriers in the channel layer, thus giving higher accumulated currents at +6 V. Compared to Schottky-gated GaN devices with a barrier built-in voltage <1 V, our device demonstrated a larger positive gate voltage (+6 V) with a low gate leakage current which is resulted from the high conduction-band offset >2 eV of HfO<sub>2</sub>/GaN [25] and the low *D*<sub>it</sub> between HfO<sub>2</sub> and GaN. A low specific on-resistance (*R*<sub>on</sub>) ~4.5 mΩ cm<sup>2</sup> was achieved even though the gate-to-source spacing was large of 3 μm and the doping concentration of channel layer was as low as 2 × 10<sup>17</sup> cm<sup>−3</sup>.

The transfer characteristics (*L*<sub>g</sub>/*W*<sub>g</sub> = 4 μm/200 μm), with *V*<sub>g</sub> sweeping from −8 V to +4 V, and for *V*<sub>d</sub> of 15 V, are shown in Fig. 2(b). The device exhibits a broad extrinsic *G*<sub>m</sub> curve, with the peak *G*<sub>m</sub> being ~31 mS/mm with *V*<sub>d</sub> of 15 V. The calculated channel mobility (*μ*<sub>n</sub>) of ~400 cm<sup>2</sup>/Vs was derived using the following equation: *μ*<sub>n</sub> = *G*<sub>m</sub> (*L*<sub>g</sub>/*W*<sub>g</sub>) / *N*<sub>d</sub> *T*<sub>ch</sub>, where *N*<sub>d</sub> and *T*<sub>ch</sub> are the doping concentration and the thickness of the channel layer [17]. An *I*<sub>on</sub>/*I*<sub>off</sub> ratio was extracted to be ~10<sup>2</sup> with a high off-state drain current (*I*<sub>off</sub>) of 10<sup>−6</sup> A/μm at a *V*<sub>d</sub> of 15 V. The channel leakage currents, resulted from the undoped GaN layer with unintentional donor doping concentration of ~10<sup>16</sup> cm<sup>−3</sup>, may have caused high *I*<sub>off</sub>, which can be improved by inserting a *p*-type GaN layer under the *n*-channel layer as a junction barrier to reduce the additional channel leakage currents.

A *D*<sub>it</sub> was calculated to be around (5–8) × 10<sup>11</sup> cm<sup>−2</sup> eV<sup>−1</sup> near conduction-band minimum of GaN using the conductance method,

Fig. 2. (a) Drain *I*-*V* characteristic for a 4 μm gate-length GaN MOSFET with a 14.8 nm ALD-HfO<sub>2</sub> as a gate dielectric; and (b) transconductance (*G*<sub>m</sub>) and drain current as a function of gate bias at a drain voltage of 15 V, with the inset showing C-V hysteresis measured at 100 kHz for the Al/HfO<sub>2</sub>/GaN MOS capacitor.

based on capacitance–voltage (C–V) characteristics of Al/HfO<sub>2</sub>/GaN MOS capacitor, which exhibited clear accumulation, depletion, deep depletion behavior, and small hysteresis of 160 mV (shown in the inset of Fig. 2(b)). The well-behaved C–V characteristics and a low *D*<sub>it</sub> indicate the high-quality interface of HfO<sub>2</sub>/GaN.

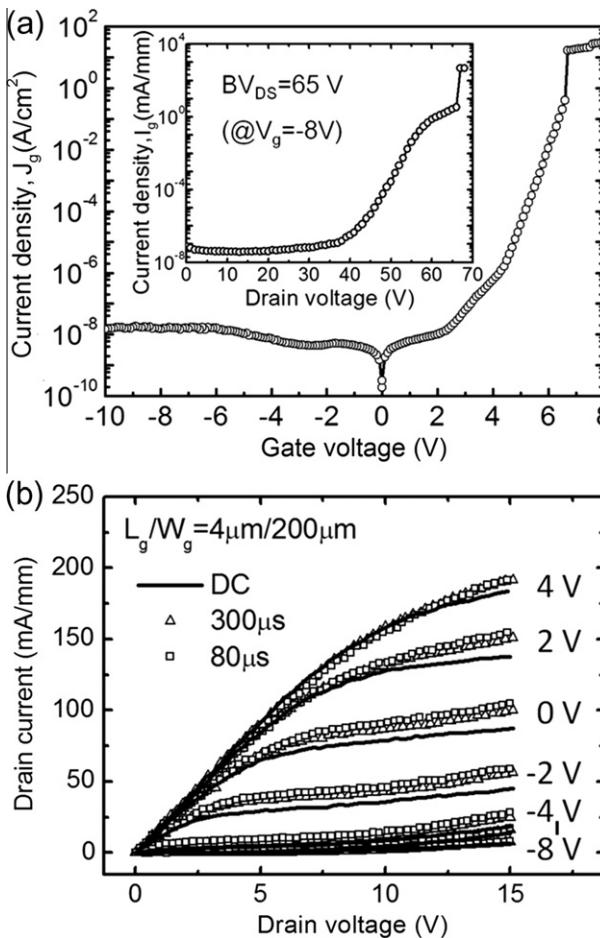

The gate-to-drain, gate leakage current density (*J*<sub>g</sub>) as a function of gate voltage of the device was measured by grounding the drain, and sweeping *V*<sub>g</sub> from −10 V to +8 V. The very low *J*<sub>g</sub> of 10<sup>−8</sup> A/cm<sup>2</sup>

Fig. 1. (a) Schematic device structure of fabricated accumulation-type GaN MOSFET; (b) planar view of ring-gate MOSFET structure.

at  $V_g$  varying from  $-10$  V to  $+2$  V was achieved (Fig. 3(a)) and is significantly lower than that of the Schottky-gate GaN devices by at least five orders of magnitude at  $V_g > +1$  V. Even at the gate voltage of  $+6$  V, the device also provides the gate leakage current density as low as  $10^{-2}$  A/cm<sup>2</sup>. The low gate leakage current reveals the high-quality and robustness of the HfO<sub>2</sub>/GaN heterostructure after  $600$  °C annealing. The oxide breakdown voltage is  $6.5$  V, corresponding to an electrical breakdown field of  $4.4$  MV/cm. In addition, the measured  $I_g$ - $V_d$  characteristics of the GaN MOSFET's under the off-state gate bias condition ( $V_g = -8$  V) is also shown in the inset of Fig. 3(a). The extremely low  $I_g \sim 10^{-8}$  mA/mm was observed even at  $V_d$  over  $30$  V. The three-terminal breakdown voltage ( $BV_{DS}$ ) of the GaN MOSFET is more than  $60$  V even with the gate-to-drain spacing of  $3$   $\mu$ m. The high  $BV_{DS}$  value is also an evidence of a high-quality HfO<sub>2</sub>/GaN interface that has sustained the high electrical fields.

The pulsed  $I$ - $V$  measurements with different pulse widths of  $80$   $\mu$ s and  $300$   $\mu$ s were performed to analyze the current collapse on the device, and are shown in Fig. 3(b) along with that of DC condition. No significant current collapse was observed in both pulse  $I$ - $V$  curves, as evidenced by the negligible dispersion between DC and pulsed  $I$ - $V$  curves in the knee region, and no  $I_d$  reduction of both pulsed  $I$ - $V$  curves in the saturation region. This observation strongly indicates the effective surface passivation of GaN using ALD-HfO<sub>2</sub>, that has decreased the surface states at the region between the gate and drain electrodes. An increased  $I_d$  of pulsed  $I$ - $V$  curves was observed which is due to the relieving of self-

Fig. 3. (a) Gate leakage current density ( $J_g$ ) vs gate voltage for GaN MOSFET, with the  $I_g$ - $V_d$  characteristics under the off-state gate bias plotted in the inset; (b) pulsed  $I$ - $V$  characteristics with pulse widths of  $300$   $\mu$ s and  $80$   $\mu$ s.

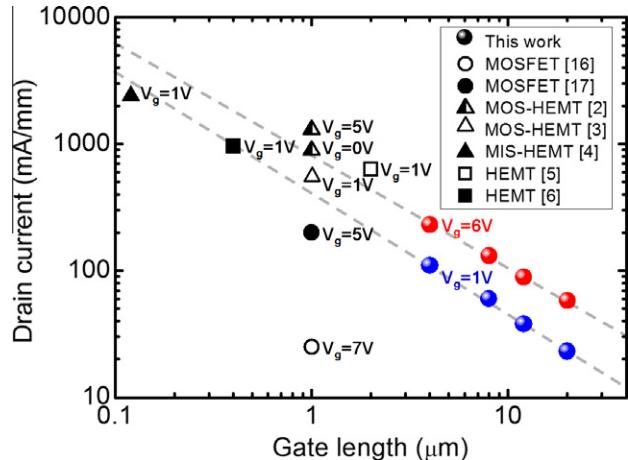

Fig. 4. Summary of maximum drain current vs. gate length of representative work on GaN-based devices.

heating effect occurring under high drain bias. In addition, the pulsed  $I$ - $V$  curve with a shorter pulse width of  $80$   $\mu$ s shows a higher  $I_d$  in the saturation region which also manifests the existence of self-heating effect.

Maximum drain currents of representative GaN-based MOSFET, MOS-HEMT, and HEMT devices are summarized in Fig. 4 [2–6,16,17]. This work has achieved  $I_d$  of  $230$  mA/mm and  $G_m$  of  $31$  mS/mm, compared favorably to those of previously reported GaN MOSFET's [15–21]. In particular, the drain current achieved in our  $4$   $\mu$ m-gate-length device is comparable to that of the  $1$   $\mu$ m-gate-length GaN MOSFET using ALD-Al<sub>2</sub>O<sub>3</sub> as a gate dielectric [17]. The measured drain currents in our GaN MOSFET's are scaled with gate lengths under  $V_g = 6$  V and  $V_g = 1$  V with  $V_d = 20$  V. For a simple linear extrapolation, we expect to have the maximum drain current of  $800$  mA/mm under  $V_g = 6$  V and  $450$  mA/mm under  $V_g = 1$  V for  $1$   $\mu$ m gate-length device, respectively, not considering parasitic resistance and short-channel effect; this is comparable to the results of the state-of-the-art GaN-based HEMT's [2–6] and higher than those of the previous reported accumulation-type GaN MOSFET's [16,17]. Nevertheless, the simply-designed HfO<sub>2</sub>/GaN MOSFET's provides extremely low gate leakage currents and negligible current collapse.

In summary, we have demonstrated accumulation-type GaN MOSFET's using ALD-HfO<sub>2</sub> as a gate dielectric with high drain current and negligible current collapse. The large dielectric constant of HfO<sub>2</sub> and high-quality HfO<sub>2</sub>/GaN interface have attributed to the high device performance. Notice that the device structure is simple. These results presented in this work have shown that GaN MOSFET's also have excellent potential for high-power RF application.

## Acknowledgments

The authors thank the National Science Council, Taiwan, under the grants of NSC-97-2120-M-007-008 and NSC-97-3114-M-007-001 for supporting this work, and also acknowledge the support from the Asian Office of Aerospace Research and Development of the US Air Force.

## References

- [1] D. Ducatteau, A. Minko, V. Hoël, E. Morvan, E. Delos, B. Grimbert, H. Lahreche, P. Bove, C. Gaquière, J.C. De Jaeger, S. Delage, IEEE Electron. Device Lett. 27 (2006) 7.

- [2] Z.H. Liu, G.I. Ng, S. Arulkumaran, Y.K.T. Maung, K.L. Teo, S.C. Foo, V. Sahmuganathan, Appl. Phys. Lett. 95 (2009) 223501.

[3] J.X. Shi, L.F. Eastman, X.B. Xin, M. Pophristic, *Appl. Phys. Lett.* 95 (2009) 042103.

[4] N. Nidhi, S. Dasgupta, D.F. Brown, S. Keller, J.S. Speck, U.K. Mishra, *Tech. Dig. – Int. Electron. Devices Meet.* 15 (2009) 955.

[5] J.W. Chung, E.L. Piner, T. Palacios, *IEEE Electron. Device Lett.* 30 (2009) 113.

[6] C.Y. Chang, S.J. Pearson, C.F. Lo, F. Ren, I.I. Kravchenko, A.M. Dabiran, A.M. Wowchak, B. Cui, P.P. Chow, *Appl. Phys. Lett.* 94 (2009) 263505.

[7] K. Matocha, T.P. Chow, R.J. Gutmann, *IEEE Electron. Device Lett.* 23 (2002) 79.

[8] Y.C. Chang, H.C. Chiu, Y.J. Lee, M.L. Huang, K.Y. Lee, M. Hong, Y.N. Chiu, J. Kwo, Y.H. Wang, *Appl. Phys. Lett.* 90 (2007) 232904.

[9] C. Liu, E.F. Chor, L.S. Tan, *Appl. Phys. Lett.* 88 (2006) 173504.

[10] K.T. Lee, C.F. Huang, J. Gong, B.H. Liou, *IEEE Electron. Device Lett.* 30 (2009) 907.

[11] P.D. Ye, B. Yang, K.K. Ng, J. Bude, G.D. Wilk, S. Halder, J.C.M. Hwang, *Appl. Phys. Lett.* 86 (2005) 063501.

[12] W.H. Chang, C.H. Lee, Y.C. Chang, P. Chang, M.L. Huang, Y.J. Lee, C.H. Hsu, J.M. Hong, C.C. Tsai, J. Kwo, M. Hong, *Adv. Mater.* 21 (2009) 4970.

[13] Y.C. Chang, Y.J. Lee, Y.N. Chiu, T.D. Lin, S.Y. Wu, H.C. Chiu, J. Kwo, Y.H. Wang, M. Hong, *J. Cryst. Growth* 301–302 (2007) 390.

[14] J. Kim, R. Mehandru, B. Luo, F. Ren, B.P. Gila, A.H. Onstine, C.R. Abernathy, S.J. Pearson, Y. Irokawa, *Appl. Phys. Lett.* 80 (2002) 4555.

[15] F. Ren, M. Hong, S.N.G. Chu, M.A. Marcus, M.J. Schurman, A. Baca, S.J. Pearson, C.R. Abernathy, *Appl. Phys. Lett.* 73 (1998) 3893.

[16] J.W. Johnson, B. Luo, F. Ren, B.P. Gila, W. Krishnamoorthy, C.R. Abernathy, S.J. Pearson, J.I. Chyi, T.E. Nee, C.M. Lee, C.C. Chuo, *Appl. Phys. Lett.* 77 (2000) 3230.

[17] Y.Q. Wu, P.D. Ye, G.D. Wilk, B. Yang, *Mater. Sci. Eng. B* 135 (2006) 282.

[18] A. Pérez-Tomás, M. Placidi, N. Baron, S. Chenot, Y. Cordier, J.C. Moreno, *J. Appl. Phys.* 106 (2009) 074519.

[19] H.B. Lee, H.I. Cho, H.S. An, Y.H. Bae, M.B. Lee, J.H. Lee, S.H. Hahn, *IEEE Electron. Device Lett.* 27 (2006) 81.

[20] Y.C. Chang, W.H. Chang, H.C. Chiu, L.T. Tung, C.H. Lee, K.H. Shiu, M. Hong, J. Kwo, J.M. Hong, C.C. Tsai, *Appl. Phys. Lett.* 93 (2008) 053504.

[21] W. Huang, T. Khan, T.P. Chow, *IEEE Electron. Device Lett.* 27 (2006) 796.

[22] Y. Xuan, H.C. Lin, P.D. Ye, *IEEE Trans. Electron. Devices* 54 (2007) 1811.

[23] Y.C. Chang, M.L. Huang, K.Y. Lee, Y.J. Lee, T.D. Lin, M. Hong, J. Kwo, T.S. Lay, C.C. Liao, K.Y. Cheng, *Appl. Phys. Lett.* 92 (2008) 072901.

[24] Y.L. Huang, P. Chang, Z.K. Yang, Y.J. Lee, H.Y. Lee, H.J. Liu, J. Kwo, J.P. Mannaerts, M. Hong, *Appl. Phys. Lett.* 86 (2005) 191905.

[25] T.E. Cook Jr., C.C. Fulton, W.J. Mecouch, R.F. Davis, G. Lucovsky, R.J. Nemanich, *J. Appl. Phys.* 94 (2003) 7155.