# High current density InN/AlN heterojunction field-effect transistor with a $\text{SiN}_x$ gate dielectric layer

Yu-Syuan Lin, Shun-Hau Koa, Chih-Yuan Chan, and Shawn S. H. Hsu<sup>a)</sup>

*Institute of Electronics Engineering, National Tsing-Hua University, Hsinchu 300, Taiwan, Republic of China*

Hong-Mao Lee and Shangjr Gwo

*Department of Physics, National Tsing-Hua University, Hsinchu 300, Taiwan, Republic of China*

(Received 28 January 2006; accepted 28 February 2007; published online 5 April 2007)

InN/AlN metal-insulator-semiconductor heterojunction field-effect transistors with a gate-modulated drain current and a clear pinch-off characteristic have been demonstrated. The devices were fabricated using high-quality InN (26 nm)/AlN (100 nm) epilayers grown by plasma-assisted molecular-beam epitaxy on Si (111) substrates. The devices exhibited a current density higher than  $\sim 530 \text{ mA/mm}$  with a  $5 \mu\text{m}$  gate length. The pinch-off voltage was at  $\sim -7 \text{ V}$  with an associated drain leakage current less than  $10 \mu\text{A/mm}$ . The observed high current density may be attributed to the high sheet carrier density due to the large spontaneous polarization difference between InN and AlN. © 2007 American Institute of Physics. [DOI: [10.1063/1.2719223](https://doi.org/10.1063/1.2719223)]

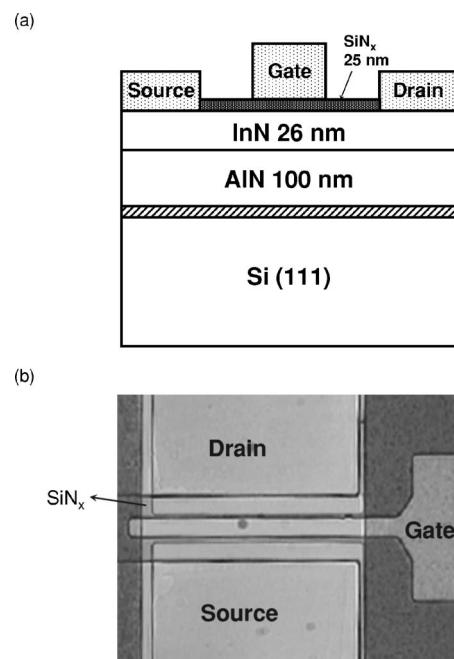

Indium nitride (InN) has been predicted to be a very promising semiconductor material for high-speed electronic devices owing to its superior electron transport properties such as small effective mass, high mobility, and large drift velocity.<sup>1–6</sup> Indeed, the existence of electrons in InN with velocities up to  $2 \times 10^8 \text{ cm/s}$ , significantly larger than those observed for other III-V semiconductors, has been verified by using the technique of transient Raman spectroscopy.<sup>7</sup> To date, the experimental demonstration of InN-based electronic devices has not yet been reported due to the difficulty in growing high-quality InN-based heterostructures. The recent advance in molecular-beam epitaxy (MBE) growth of commensurately matched InN epitaxial layers on the *c*-plane AlN or GaN surface has significantly changed this situation, allowing for the design of InN-based heterojunction field-effect transistors (HFETs).<sup>8–10</sup> However, there are still many challenges that remained to be realized the InN-based HFETs, which include the inability to form Schottky contacts,<sup>11</sup> the lack of demonstrated dielectric layer, and the strong intrinsic accumulation of electrons on the InN surface.<sup>12,13</sup> In this study, we utilize a metal-insulator-semiconductor (MIS) structure for the demonstration of InN-based metal-insulator-semiconductor heterojunction field-effect transistors (MISHFETs), as shown in Fig. 1(a). Figure 1(b) shows the micrograph of the fabricated device with the gate, source, and drain terminals labeled in the figure. A thin film of  $\text{SiN}_x$  was employed as the insulator between the InN channel and the Ni/Au gate. The measured results indicate that an extremely high density of electrons exists in the channel, resulting in a high drain current. Most importantly, we demonstrate that the current can be modulated by varying the gate voltage with a clear pinch-off characteristic.

The device layer of nitrogen-polarity InN(0001̄) was grown on the Si(111) substrate by nitrogen-plasma-assisted MBE with a 120 nm AlN(0001̄) buffer layer.<sup>8</sup> We have confirmed that the transition from pseudomorphic to 8:9 commensurate lattice match occurs within the first monolayer

growth of InN on AlN. This allows the formation of commensurate and nearly strain-free heterointerface with a common 8:9 two-dimensional superlattice, in which every eight-unit cell of InN aligns exactly with every nine-unit cell of AlN.<sup>9</sup> The nitrogen-polarity InN layer thickness was designed as 26 nm to achieve the electrical modulation of drain current, while if the layer is too thick, the device cannot be pinched off before the breakdown occurs. An *n*-type carrier concentration of  $\sim 4.2 \times 10^{19} \text{ cm}^{-3}$  and a mobility of  $\sim 209 \text{ cm}^2/\text{V s}$  were obtained by standard Hall measurements at room temperature for the InN films used in this study. In contrast to higher mobility ( $>1000 \text{ cm}^2/\text{V s}$ ) exhibited in thick films ( $>1 \mu\text{m}$ ), the smaller mobility results

FIG. 1. (a) Cross section of the InN/AlN MISHFET grown on the Si (111) substrate. The hatched region between AlN and Si(111) represents an ultra-thin  $\text{Si}_3\text{N}_4$  layer formed by plasma nitridation prior to the growth of III-nitride layers. (b) Micrograph of the fabricated InN/AlN MISHFET.

<sup>a)</sup>Electronic mail: shhsu@ee.nthu.edu.tw

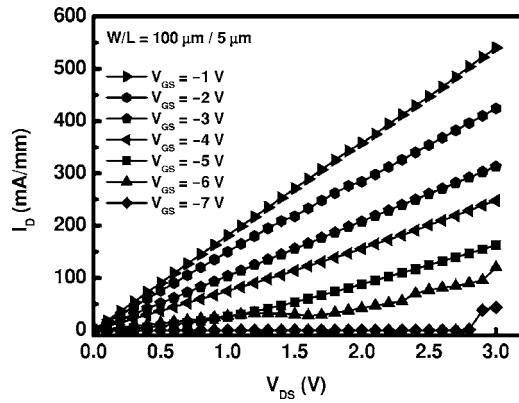

FIG. 2. Measured dc current-voltage characteristics of the InN/AlN MISHFET.

from increasing effects of surface and interface.

The first step of device fabrication was to define the active region. Device isolation was achieved by the inductively coupled plasma etching with a  $\text{Cl}_2/\text{Ar}$  gas mixture, where Ni served as a hard mask to protect the device area. A 25 nm  $\text{SiN}_x$  layer was deposited by plasma-enhanced chemical vapor deposition as the gate dielectric layer. High-quality Ohmic contacts of both drain and source were formed by Ti (30 nm)/Al (200 nm) deposited by e-beam evaporation without the need of rapid thermal annealing procedure due to the inherently high surface charge density of the material. The measured contact resistance by the transmission line model approach was below  $0.5 \Omega \text{ mm}$ . Finally, the gate metal of Ni (30 nm)/Au (300 nm) was deposited also by e-beam evaporation.

Figure 2 is the measured dc  $I_{\text{D}}-V_{\text{DS}}$  characteristics of an InN/AlN MISHFET with a gate length of 5  $\mu\text{m}$  and a width of 100  $\mu\text{m}$ . A clear gate-controlled current-voltage characteristic can be observed. The peak current density of the 5  $\mu\text{m}$  gate InN/AlN MISHFETs is  $\sim 530 \text{ mA/mm}$  under a gate bias of  $-1 \text{ V}$  and a drain bias of 3 V. Assuming that the drain current is inversely proportional to the gate length, the observed current density is much higher than that typically obtained from GaN-based high electron mobility transistors.<sup>14</sup> The pinch-off voltage is  $\sim -7 \text{ V}$  and the associated drain leakage current is smaller than  $10 \mu\text{A/mm}$ . The results can be further analyzed by using the equation for a long-channel FET:

$$I_{\text{D}} = q\mu n_s \frac{W}{L} V_{\text{DS}}, \quad (1)$$

where  $I_{\text{D}}$  is the drain current,  $q$  is the electron charge,  $\mu$  is the mobility of free electrons,  $n_s$  is the total sheet carrier concentration,  $W$  is the device width, and  $L$  is the gate length. Based on Eq. (1), the calculated sheet carrier density  $n_s$  is as high as  $2.6 \times 10^{13} \text{ cm}^{-2}$ . Compared with the  $n_s$  for traditional GaN-based HFETs with a typical sheet carrier density of  $\sim 1 \times 10^{13} \text{ cm}^{-2}$ ,<sup>15-17</sup> the calculated result suggests that the InN-based device has a much higher carrier density. This can be attributed to the large spontaneous polarization difference between nitrogen-polarity InN and AlN epitaxial layers,<sup>9,10,18,19</sup> leading to a high current density as observed here. In our recent work, we have measured large band offset values formed between commensurately matched InN/AlN (both AlN and InN lattices are near completely relaxed, thereby the piezoelectric effect is negligible),<sup>10</sup> which can

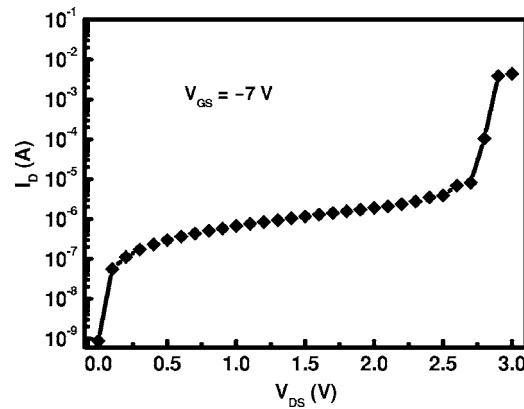

FIG. 3. Off-state breakdown characteristics of the InN/AlN MISHFET.

also contribute to the high carrier density at the heterojunction (accumulated from the InN epilayer side).

One may notice that the current saturation characteristic in the measured  $I_{\text{D}}-V_{\text{DS}}$  curve was not clearly observed in Fig. 2. We found that breakdown occurred before the device can enter the saturation region during the measurements. Figure 3 highlights the off-state drain to source breakdown characteristic of the device, which is about 2.7 V at a gate bias of  $-7 \text{ V}$ . The relatively small breakdown voltage may be attributed to the small band gap of InN (0.6–0.7 eV).<sup>20,21</sup> As an approximation to simplify the analysis here, we use the following equation for metal-semiconductor field-effect transistors to estimate the required drain-source voltage ( $V_{\text{DS},\text{sat}}$ ) for the device to enter the saturation region:<sup>22</sup>

$$V_{\text{DS},\text{sat}} = \frac{qN_e}{2\epsilon_s} a^2 - (\phi_{\text{FB}} - V_{\text{GS}}), \quad (2)$$

where the InN layer thickness  $a$  of 26 nm, the electron carrier concentration  $N_e$  of  $1.0 \times 10^{19} \text{ cm}^{-3}$  (estimate based on  $n_s = 2.6 \times 10^{13} \text{ cm}^{-2}$ ), and the dielectric constant  $\epsilon_s$  of 6.7 are used here.<sup>23</sup> In addition,  $(\phi_{\text{FB}} - V_{\text{GS}})$  describes the effective applied gate voltage from the MIS interface to the channel, where  $\phi_{\text{FB}}$  is the flatband voltage shift attributed by the gate dielectric. In this case,  $\phi_{\text{FB}}$  is relatively small and can be neglected. The calculated  $V_{\text{DS},\text{sat}}$  is 9.1 V at  $V_{\text{GS}}$  of 0 V, which is higher than the observed channel breakdown voltage.

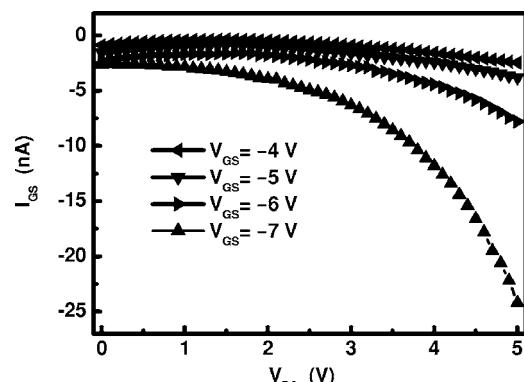

The gate leakage current  $I_{\text{GS}}$  has also been measured under different gate biases as shown in Fig. 4. As can be seen,  $I_{\text{GS}}$  is below  $\sim 25 \text{ nA}$  ( $0.25 \mu\text{A/mm}$ ) even under a

FIG. 4. Gate leakage currents as a function of  $V_{\text{DS}}$  under different gate biases of the InN/AlN MISHFET.

large drain voltage of 5 V and a gate voltage of  $-7$  V. The result suggests that the breakdown occurred in the InN channel region instead of in the gate dielectric layer. Therefore, with a relatively small band gap, an early channel breakdown occurred and the saturation characteristic was not observed in the InN-based FETs studied here.

In summary, the first result of gate-controllable  $I_D$ - $V_D$  characteristics for InN-based FETs with a  $\text{SiN}_x$  gate dielectric layer has been demonstrated. Owing to the high sheet carrier density, a high current density up to  $\sim 530$  mA/mm was achieved in a device with a 5  $\mu\text{m}$  gate length and a width of 100  $\mu\text{m}$ , which is much higher than that in conventional GaN-based devices. A clear pinch-off characteristic was observed at a gate voltage of  $-7$  V. In addition, the off-state drain to source breakdown voltage of 2.7 V was obtained. No clear saturation characteristics of the drain current were observed in these devices, and the reason can be attributed to the relatively small band gap of the pure InN material. As a consequence, the devices reached the breakdown voltage before the saturation of electrons occurred.

This work was supported in part by the National Science Council in Taiwan (Grant Nos. NSC-95-2221-E-007-256 and NSC-95-2112-M-007-008).

<sup>1</sup>S. K. O'Leary, B. E. Foutz, M. S. Shur, U. V. Bhapkar, and L. F. Eastman, *J. Appl. Phys.* **83**, 826 (1998).

<sup>2</sup>S. K. O'Leary, B. E. Foutz, M. S. Shur, and L. F. Eastman, *Appl. Phys. Lett.* **87**, 222103 (2005).

<sup>3</sup>S. K. O'Leary, B. E. Foutz, M. S. Shur, and L. F. Eastman, *Appl. Phys. Lett.* **88**, 152113 (2006).

<sup>4</sup>For a review, see S. K. O'Leary, B. E. Foutz, M. S. Shur, and L. F. Eastman, *J. Mater. Sci.: Mater. Electron.* **17**, 87 (2006).

<sup>5</sup>K. T. Tsien, W. Liang, D. K. Ferry, H. Lu, W. J. Schaff, U. Ozgur, Y. Fu, Y. T. Moon, F. Yun, H. Morkoc, and H. O. Everitt, *Superlattices Micro-*

*struct.* **38**, 77 (2005).

<sup>6</sup>K. T. Tsien, C. Poweleit, D. K. Ferry, H. Lu, and W. J. Schaff, *J. Cryst. Growth* **288**, 289 (2006).

<sup>7</sup>K. T. Tsien, C. Poweleit, D. K. Ferry, H. Lu, and W. J. Schaff, *Appl. Phys. Lett.* **86**, 222103 (2005).

<sup>8</sup>S. Gwo, C.-L. Wu, C.-H. Shen, W.-H. Chang, T. M. Hsu, J.-S. Wang, and J.-T. Hsu, *Appl. Phys. Lett.* **84**, 3765 (2004).

<sup>9</sup>C.-L. Wu, C.-H. Shen, H.-W. Lin, H.-M. Lee, and S. Gwo, *Appl. Phys. Lett.* **87**, 241916 (2005).

<sup>10</sup>C.-L. Wu, C.-H. Shen, and S. Gwo, *Appl. Phys. Lett.* **88**, 032105 (2006).

<sup>11</sup>H. Lu, W. J. Schaff, L. F. Eastman, and C. E. Stutz, *Appl. Phys. Lett.* **82**, 1736 (2003).

<sup>12</sup>K. A. Rickert, A. B. Ellis, F. J. Himpel, H. Lu, W. Schaff, J. M. Redwing, F. Dwukusuma, and T. F. Kuech, *Appl. Phys. Lett.* **82**, 3254 (2003).

<sup>13</sup>I. Mahboob, T. D. Veal, C. F. McConville, H. Lu, and W. J. Schaff, *Phys. Rev. Lett.* **92**, 036804 (2004).

<sup>14</sup>S. J. Pearton and F. Ren, *Adv. Mater. (Weinheim, Ger.)* **12**, 1571 (2000).

<sup>15</sup>J. W. Johnson, A. G. Baca, R. D. Briggs, R. J. Shul, J. R. Wendt, C. Monier, F. Ren, S. J. Pearton, A. M. Dabiran, A. M. Wowchack, C. J. Polley, and P. P. Chow, *Solid-State Electron.* **45**, 1979 (2001).

<sup>16</sup>Y. F. Wu, S. Keller, P. Kozodoy, B. P. Keller, P. Parikh, D. Kapolnek, S. P. DenBaars, and U. K. Mishra, *IEEE Electron Device Lett.* **18**, 290 (1997).

<sup>17</sup>X. Z. Dang, P. M. Asbeck, E. T. Yu, G. J. Sullivan, M. Y. Chen, B. T. McDermott, K. S. Boutros, and J. M. Redwing, *Appl. Phys. Lett.* **74**, 3890 (1999).

<sup>18</sup>E. T. Yu, G. J. Sullivan, P. M. Asbeck, C. D. Wang, D. Qiao, and S. S. Lau, *Appl. Phys. Lett.* **71**, 2794 (1997).

<sup>19</sup>O. Ambacher, J. Smart, J. R. Shealey, N. G. Weimann, K. Chu, M. Murphy, W. J. Schaff, L. F. Eastman, R. Dimitrov, L. Wittmer, M. Stutzmann, W. Rieger, and J. Hilsenbeck, *J. Appl. Phys.* **85**, 3222 (1999).

<sup>20</sup>V. Yu. Davydov, A. A. Klochikhin, R. P. Seisyan, V. V. Emtsev, S. V. Ivanov, F. Bechstedt, J. Furthmüller, H. Harima, A. V. Mudryi, J. Aderhold, O. Semchinova, and J. Graul, *Phys. Status Solidi B* **229**, R1 (2002).

<sup>21</sup>J. Wu, W. Walukiewicz, K. M. Yu, J. W. Ager III, E. E. Haller, H. Lu, W. J. Schaff, Y. Saito, and Y. Nanishi, *Appl. Phys. Lett.* **80**, 3967 (2002).

<sup>22</sup>W. Liu, *Fundamentals of III-V Devices: HBTs, MESFETs, and HFETs/HEMTs* (Wiley, New York, 1999).

<sup>23</sup>A. Kasic, E. Valcheva, B. Monemar, H. Lu, and W. J. Schaff, *Phys. Rev. B* **70**, 115217 (2004).